KCU105 Board User Guide www.xilinx.com 52

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

Tab le 1- 17 lists the CP2105GM connections to FPGA U1.

For more technical information on the CP2105GM and the VCP drivers, see the Silicon Labs

website [Ref 28].

Xilinx UART IP is expected to be implemented in the FPGA logic using IP as described in the

LogiCORE IP AXI UART Lite Product Guide (PG142) [Ref 11].

HDMI Video Output

[Figure 1-2, callout 20]

The KCU105 evaluation board provides a HDMI video output using an Analog Devices

ADV7511KSTZ-P HDMI transmitter at U52. The HDMI transmitter U52 is connected to the

XCKU040 device bank 64 and its output is provided on a Molex 500254-1927 HDMI type-A

receptacle at P6. The ADV7511 supports 1080P 60 Hz, YCbCr 4:2:2 encoding via 16-bit input

data mapping.

The KCU105 evaluation board supports these HDMI device interfaces:

• 16 data lines

•Independent VSYNC, HSYNC

• Single-ended input CLK

• Interrupt Out Pin to FPGA

•I2C

•SPDIF

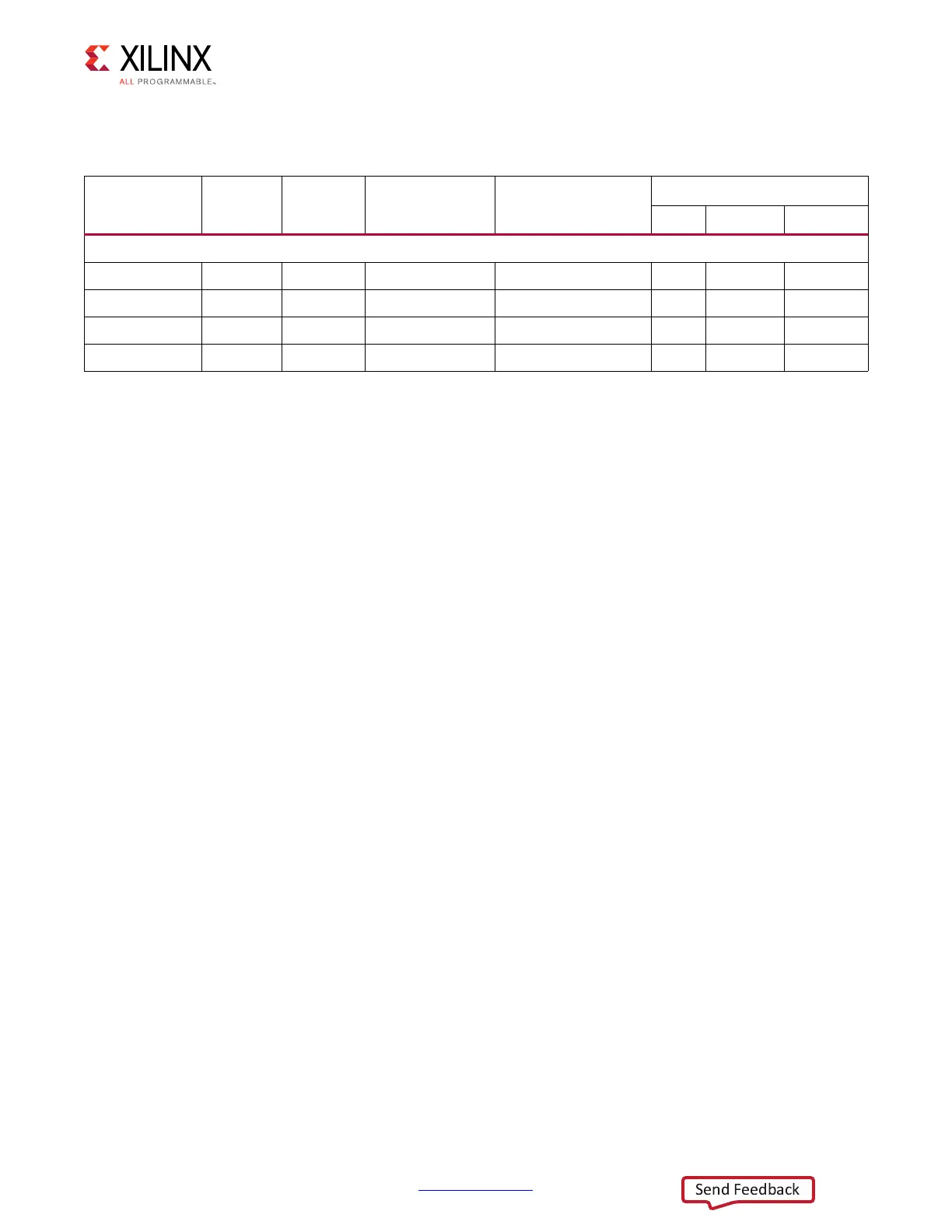

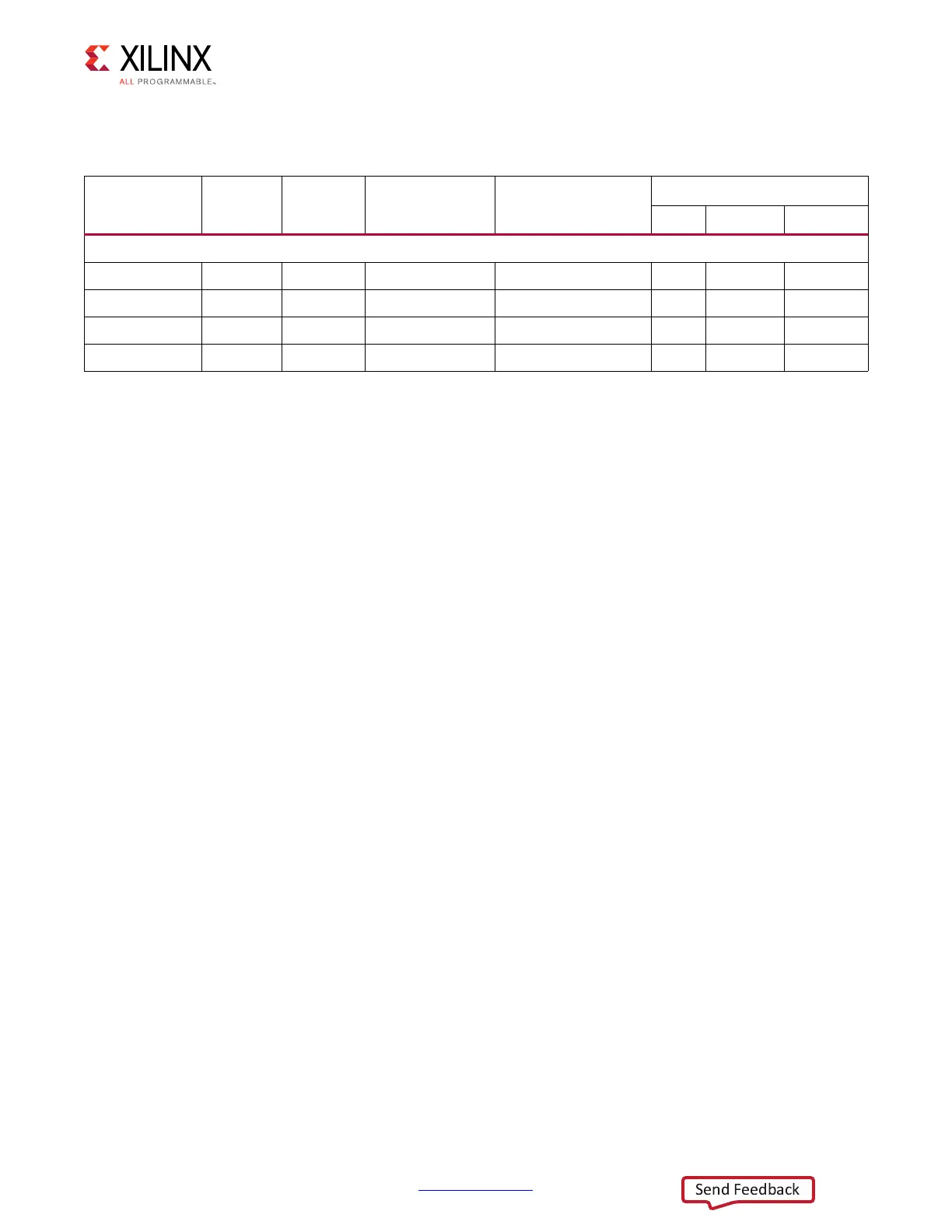

Table 1-17: FPGA U1 to CP2105GM U34 Connections

FPGA (U1) Pin Function Direction I/O Standard

Schematic Net

Name

CP2105GM Device (U34)

Pin Function Direction

XCKU040 FPGA (U1) - UART1 SCI

(1)

G25 RX Input LVCMOS18 USB_UART_TX 21 TXD Output

K26 TX Output LVCMOS18 USB_UART_RX 20 RXD Input

L23 CTS Output LVCMOS18 USB_UART_CTS 18 CTS Input

K27 RTS Input LVCMOS18 USB_UART_RTS 19 RTS Output

Notes:

1. The USB_UART_sig nets are named from the perspective of the CP2105GM device (U34).

Loading...

Loading...