Spartan-6 FPGA GTP Transceiver Wizard v1.8 www.xilinx.com 19

UG546 (v1.8) December 14, 2010

Generating the Core

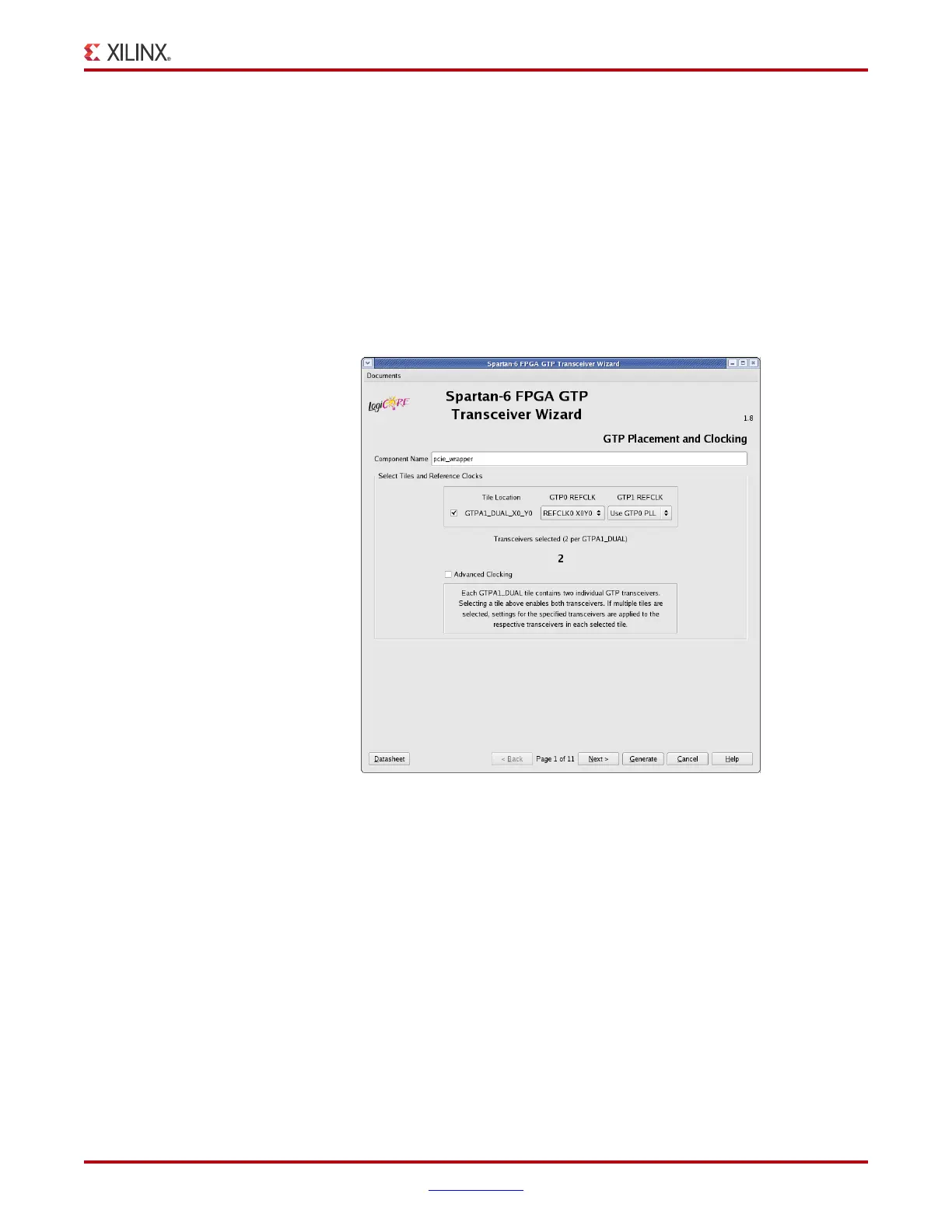

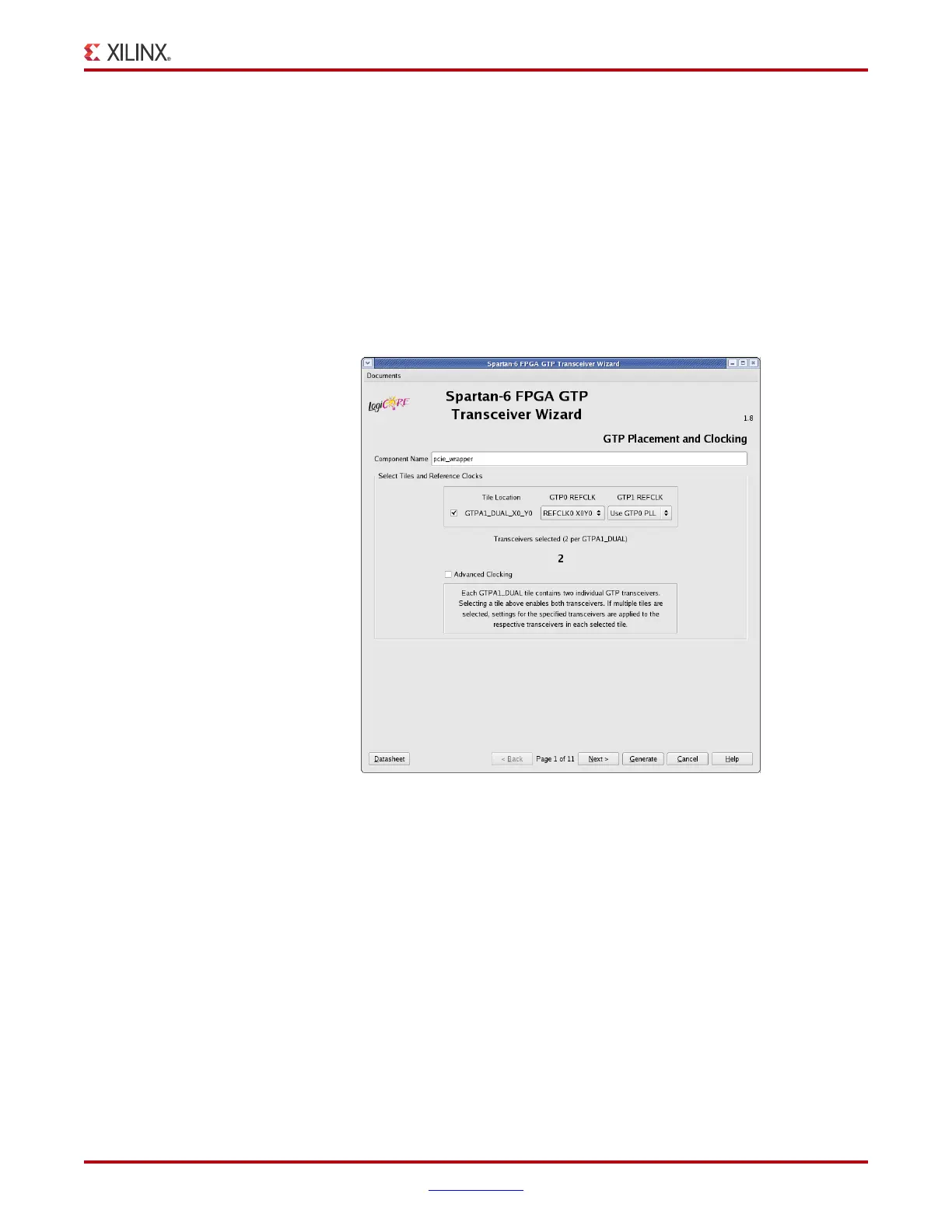

GTP Placement and Clocking

The GTP Placement and Clocking screen (page 1) of the Wizard (Figure 3-5) allows you to

select the component name and determine the placement of the GTP transceivers and the

reference clock source.

1. In the Component Name field, enter a name for the core instance. This example uses

the name pcie_wrapper.

The number of GTPA1_DUAL transceiver primitives appearing on this page depends on

the selected target device and package. The PCI EXPRESS example design uses four GTP

transceivers (two GTPA1_DUAL primitives).

Table 3-1 describes the GTP transceiver

selection and Reference Clock options.

X-Ref Target - Figure 3-5

Figure 3-5: GTP Placement and Clocking - Page 1

Loading...

Loading...