24 www.xilinx.com Spartan-6 FPGA GTP Transceiver Wizard v1.8

UG546 (v1.8) December 14, 2010

Chapter 3: Running the Wizard

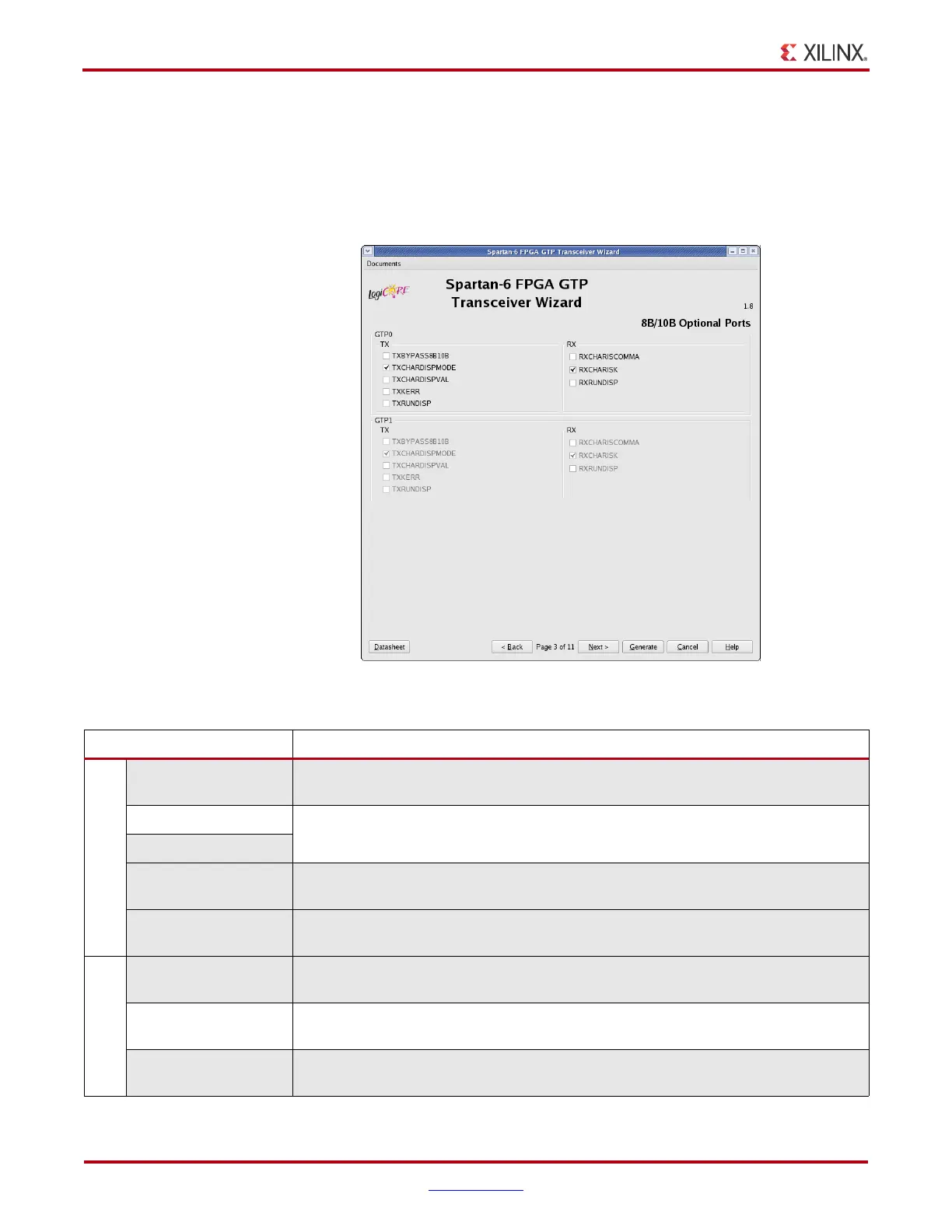

8B/10B Optional Ports

The 8B/10B Optional Ports screen (page 3) of the Wizard (Figure 3-7) provides selections

for 8B/10B-specific optional ports. Placing a check next to one of the listed optional port

names makes that port available in the wrapper for use by the application.

Table 3-6 details

the available TX and RX 8B/10B optional ports.

X-Ref Target - Figure 3-7

Figure 3-7: 8B/10B Optional Ports - Page 3

Table 3-6: 8B/10B Optional Ports

Option Description

TX

TXBYPASS8B10B

Two-bit wide port disables 8B/10B encoder on a per-byte basis. High-order bit affects

high-order byte of data path.

TXCHARDISPMODE

Two-bit wide ports control disparity of outgoing 8B/10B data. High-order bit affects

high-order byte of data path.

TXCHARDISPVAL

TXKERR

Two-bit wide port flags invalid K character codes as they are encountered. High-order

bit corresponds to high-order byte of data path.

TXRUNDISP

Two-bit wide port indicates current running disparity of the 8B/10B encoder on a per-

byte basis. High-order bit affects high-order byte of data path.

RX

RXCHARISCOMMA

Two-bit wide port flags valid 8B/10B comma characters as they are encountered. High-

order bit corresponds to high-order byte of data path.

RXCHARISK

Two-bit wide port flags valid 8B/10B K characters as they are encountered. High-order

bit corresponds to high-order byte of data path.

RXRUNDISP

Two-bit wide port indicates current running disparity of the 8B/10B decoder on a per-

byte basis. High-order bit corresponds to high-order byte of data path.

Loading...

Loading...