Spartan-6 FPGA GTP Transceiver Wizard v1.8 www.xilinx.com 39

UG546 (v1.8) December 14, 2010

Generating the Core

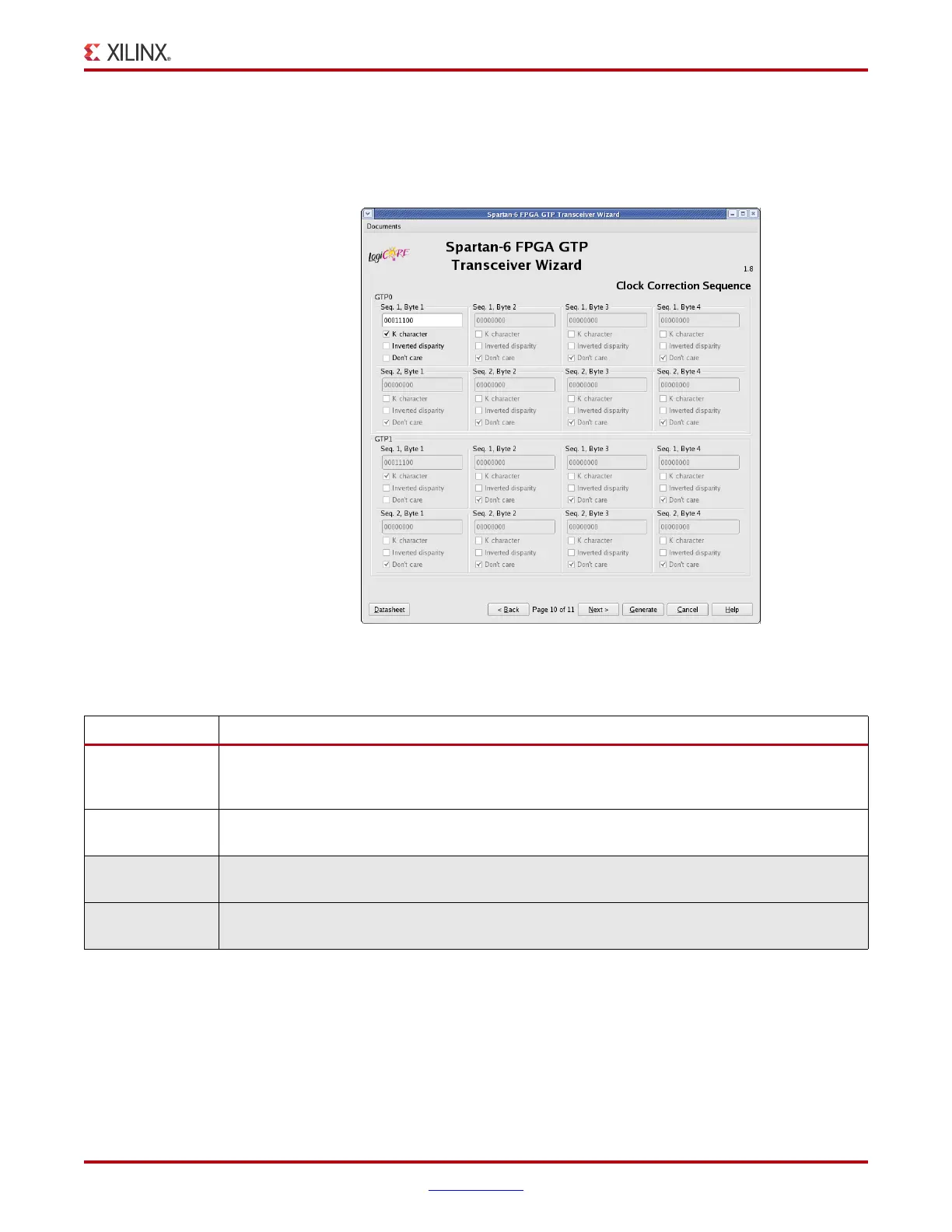

Clock Correction Sequence

The Clock Correction Sequence screen (page 10) of the Wizard (Figure 3-14) defines the

clock correction sequence. See Table 3-24 for details.

X-Ref Target - Figure 3-14

Figure 3-14: Clock Correction Sequence - Page 10

Table 3-24: Clock Correction Sequence

Option Description

Byte (Symbol)

Set each symbol to match the pattern the protocol requires. The PCI EXPRESS sequence length is 8

bits. 00011100 is used for the first symbol of sequence 1. The remaining symbols are disabled

because the Sequence length is set to 1.

K Character

This option is available when 8B/10B decoding is selected. When checked, the symbol is an 8B/10B

K character.

Inverted Disparity

Some protocols with 8B/10B decoding use symbols with deliberately inverted disparity. This

option should be checked when such symbols are expected in the sequence.

Don’t Care

Multiple-byte sequences can have wild card symbols by checking this option. Unused bytes in the

sequence automatically have this option set.

Loading...

Loading...