Spartan-6 FPGA GTP Transceiver Wizard v1.8 www.xilinx.com 27

UG546 (v1.8) December 14, 2010

Generating the Core

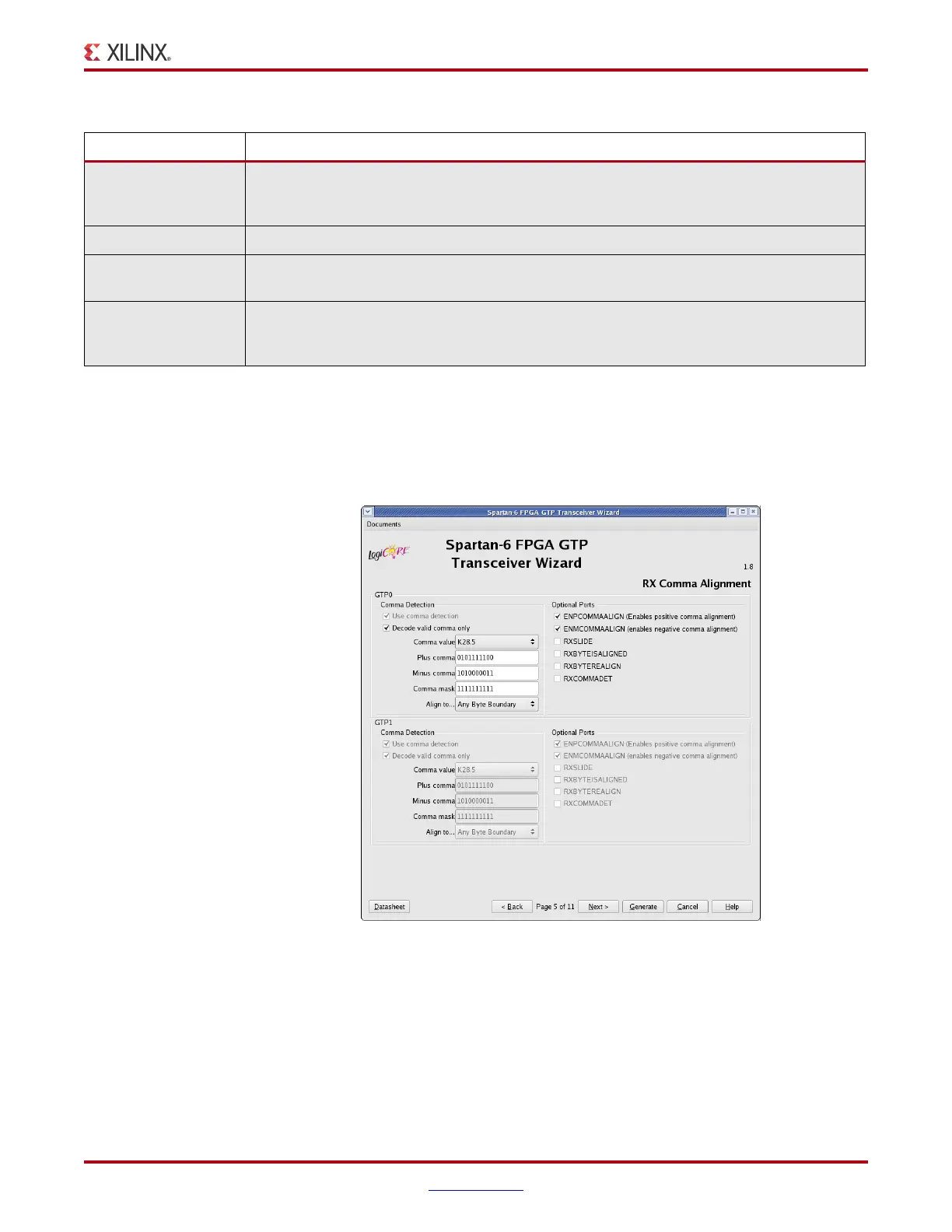

RX Comma Alignment

The RX Comma Alignment screen (page 5) of the Wizard (Figure 3-9) allows you to

configure the RX comma detection and alignment logic. The settings are detailed in

Table 3-10, page 28.

TXOUTCLK

Parallel clock signal generated by the GTP transceiver. This option is required when selected

as an input to either TXUSRCLK or RXUSRCLK. This option is not available when the TX

Phase Alignment circuit is used.

TXRESET Active-High reset signal for the transmitter PCS logic.

TXBUFSTATUS

Two-bit signal monitors the status of the TX elastic buffer. This option is not available when

the TX Phase Alignment circuit is used.

REFCLKOUT

Select this option to have the REFCLKOUT signal available to the application. Any options

selected on the following Wizard pages that require this signal causes the forced selection of

this option.

Table 3-9: Optional Ports (Cont’d)

Option Description

X-Ref Target - Figure 3-9

Figure 3-9: RX Comma Alignment - Page 5

Loading...

Loading...