Virtex-6 FPGA Connectivity Kit Getting Started www.xilinx.com 73

UG664 (v1.4) July 6, 2011

Getting Started with the Virtex-6 FPGA IBERT Reference Design

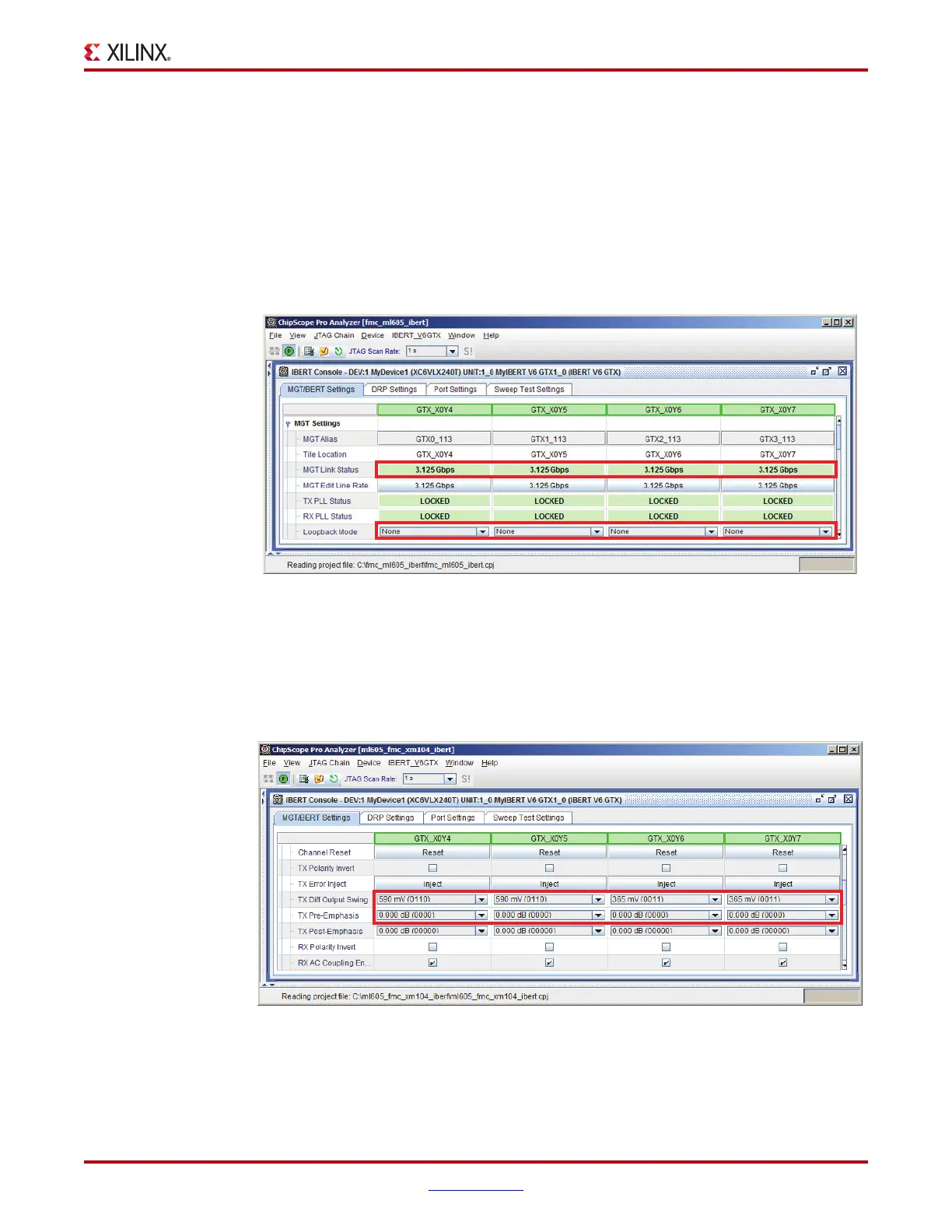

13. Verify the line rates for the GTX transceivers (see Figure 76):

a. The line rate is set to 3.125 Gb/s for all four GTX transceiver channels instantiated

in the design.

b. The GTX0_113 and GTX1_113 transceiver channels have been looped on external

loopback through a SATA cable. Select the loopback mode for these transceiver

channels as None (no internal loopback). The GTX2_113 and GTX3_113

transceiver channels have been looped on external loopback through an SMA

cable. Select the loopback mode for these transceiver channels as None (no

internal loopback).

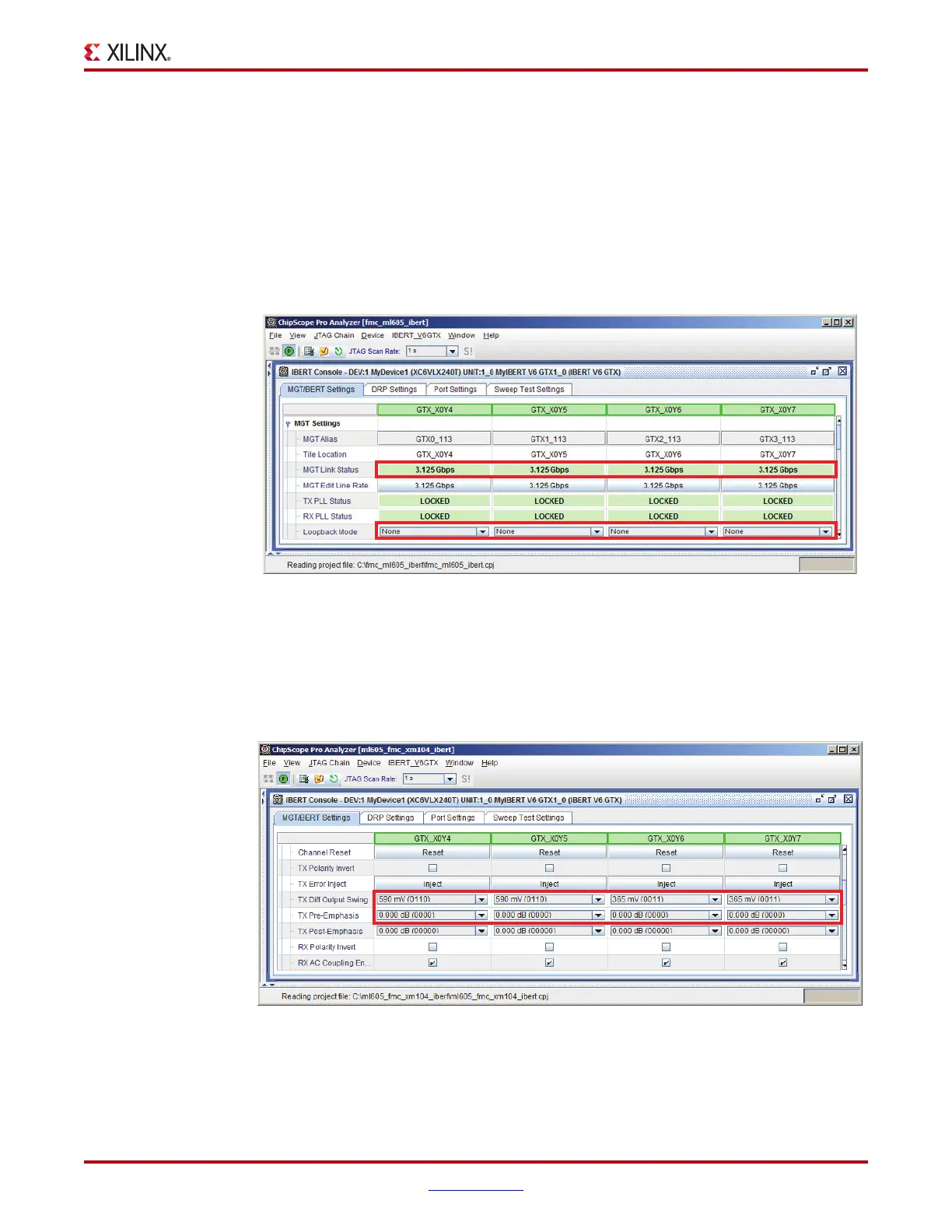

14. Configure the GTX transmit parameter settings (see Figure 77):

a. Set the TX Diff Output Swing parameter to 590 mV (0110) for the SATA channels

and 365 mV for the SMA channels.

b. Set the TX Pre-Emphasis parameter to 0 dB (000).

X-Ref Target - Figure 76

Figure 76: Verify the GTX Transceiver Loopback Configuration and Link Status

X-Ref Target - Figure 77

Figure 77: Modifying the Transmitter Settings of the GTX Transceiver Channels

Loading...

Loading...