72 www.xilinx.com Virtex-6 FPGA Connectivity Kit Getting Started

UG664 (v1.4) July 6, 2011

Getting Started with the Virtex-6 FPGA IBERT Reference Design

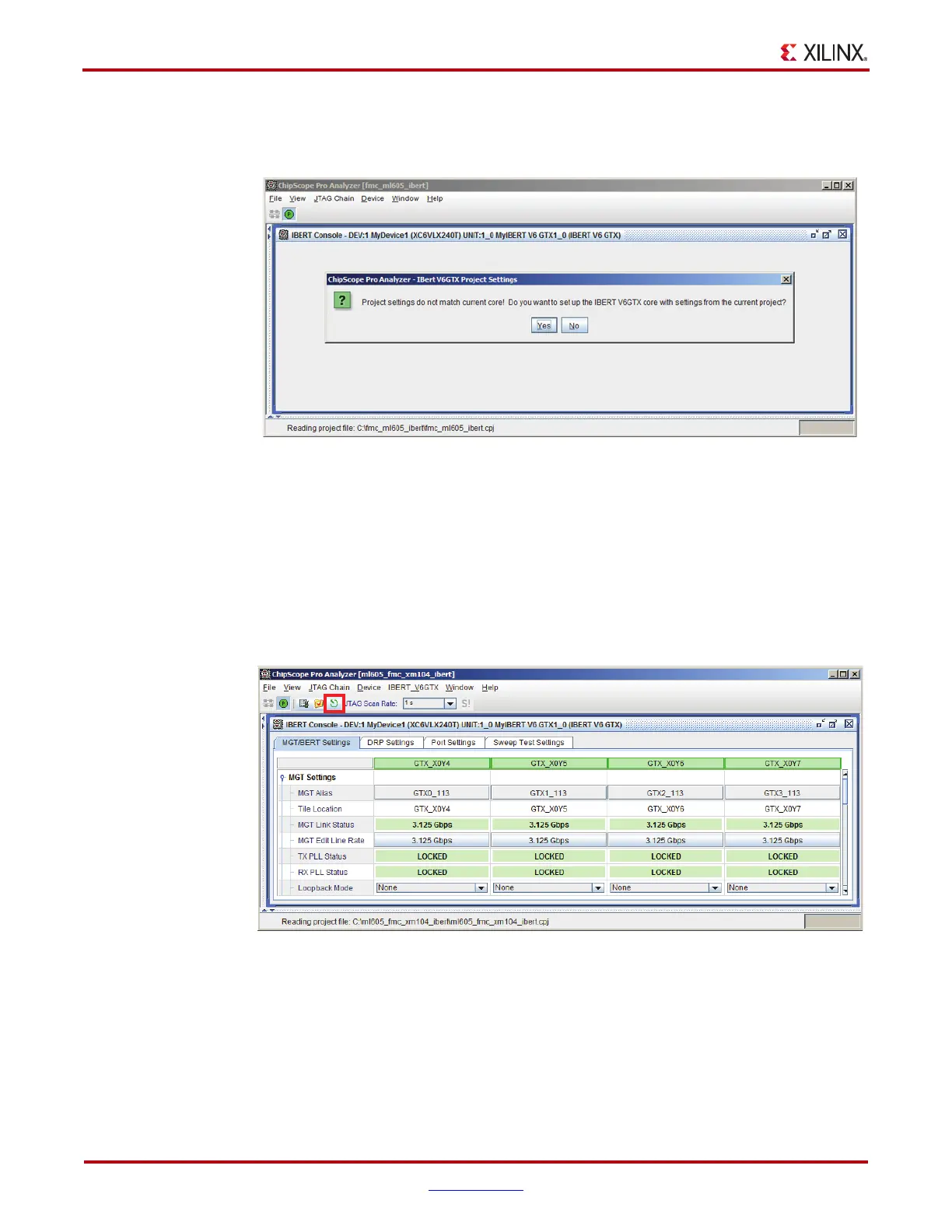

11. Load the ChipScope Pro Analyzer project:

a. Click Yes on the dialog box shown in Figure 74.

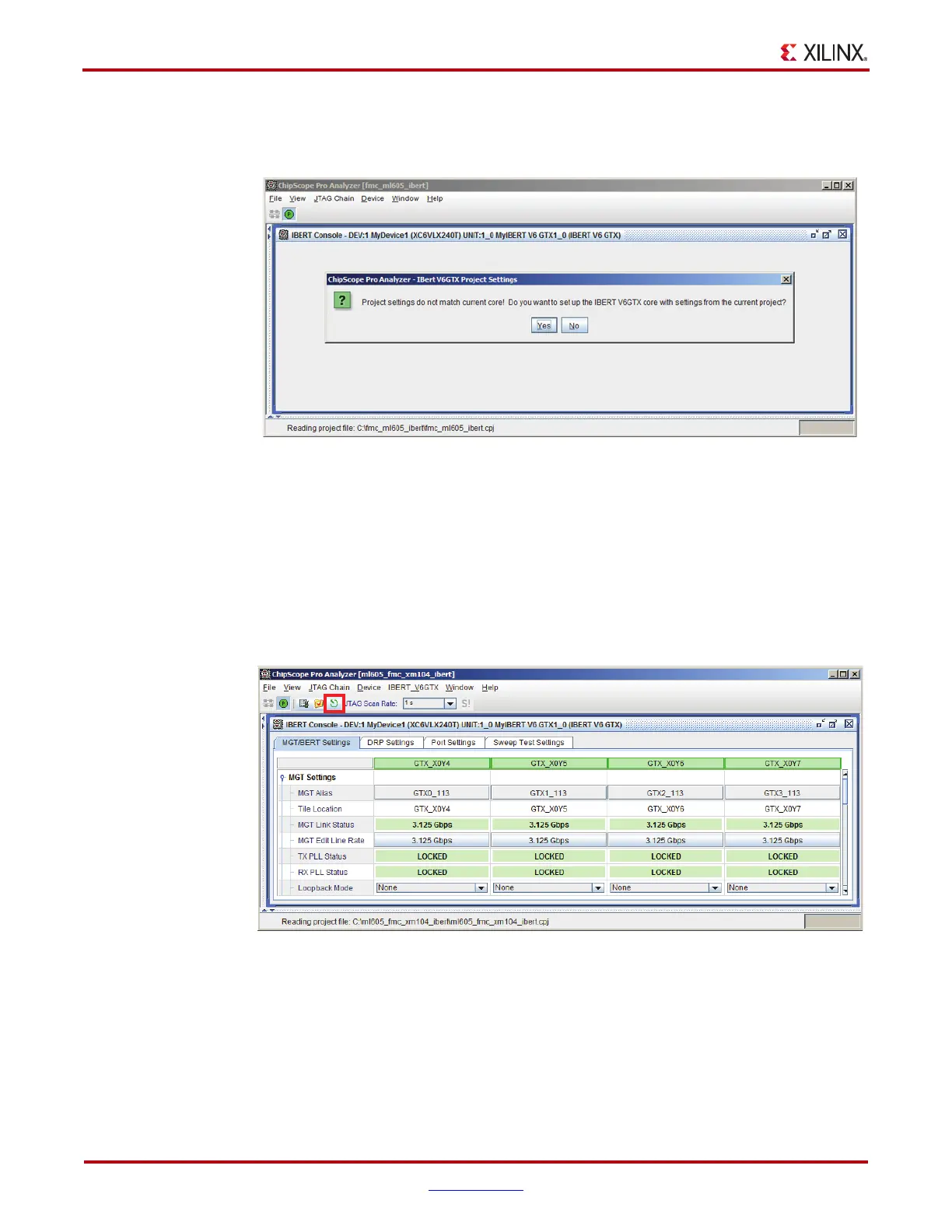

12. Load and reset the IBERT reference design through the GUI (see Figure 75).

GTX0_113 FMC Daughter Card connector: DP3 SATA2 Host Channel

GTX1_113 FMC Daughter Card connector: DP2 SATA1 Host Channel

GTX2_113 FMC Daughter Card connector: DP1 SMA Channel

GTX3_113 FMC Daughter Card connector: DP0 SMA Channel

X-Ref Target - Figure 74

Figure 74: Load the ChipScope Tool Project and Communicate with the IBERT

Reference Design

X-Ref Target - Figure 75

Figure 75: Load and Reset the IBERT Reference Design

UG664_52_021810

Loading...

Loading...