Virtex-6 FPGA Connectivity Kit Getting Started www.xilinx.com 75

UG664 (v1.4) July 6, 2011

Reference Design Files

Reference Design Files

The design checklist in Table 2 includes simulation, implementation, and hardware details

for the reference designs. After registration, reference design files are available for

download at ug664.zip

.

Installation is Complete

The Xilinx design tools have been successfully installed, the CORE Generator tool flow for

IP delivery is better understood, and the FPGA application is ready to be designed and

implemented targeting the Virtex-6 LXT architecture.

For updated information on this Virtex-6 FPGA Connectivity Kit, go to

http://www.xilinx.com/v6connkit

. Check this page regularly for the latest in

documentation, FAQs, reference design examples, product updates, and known issues.

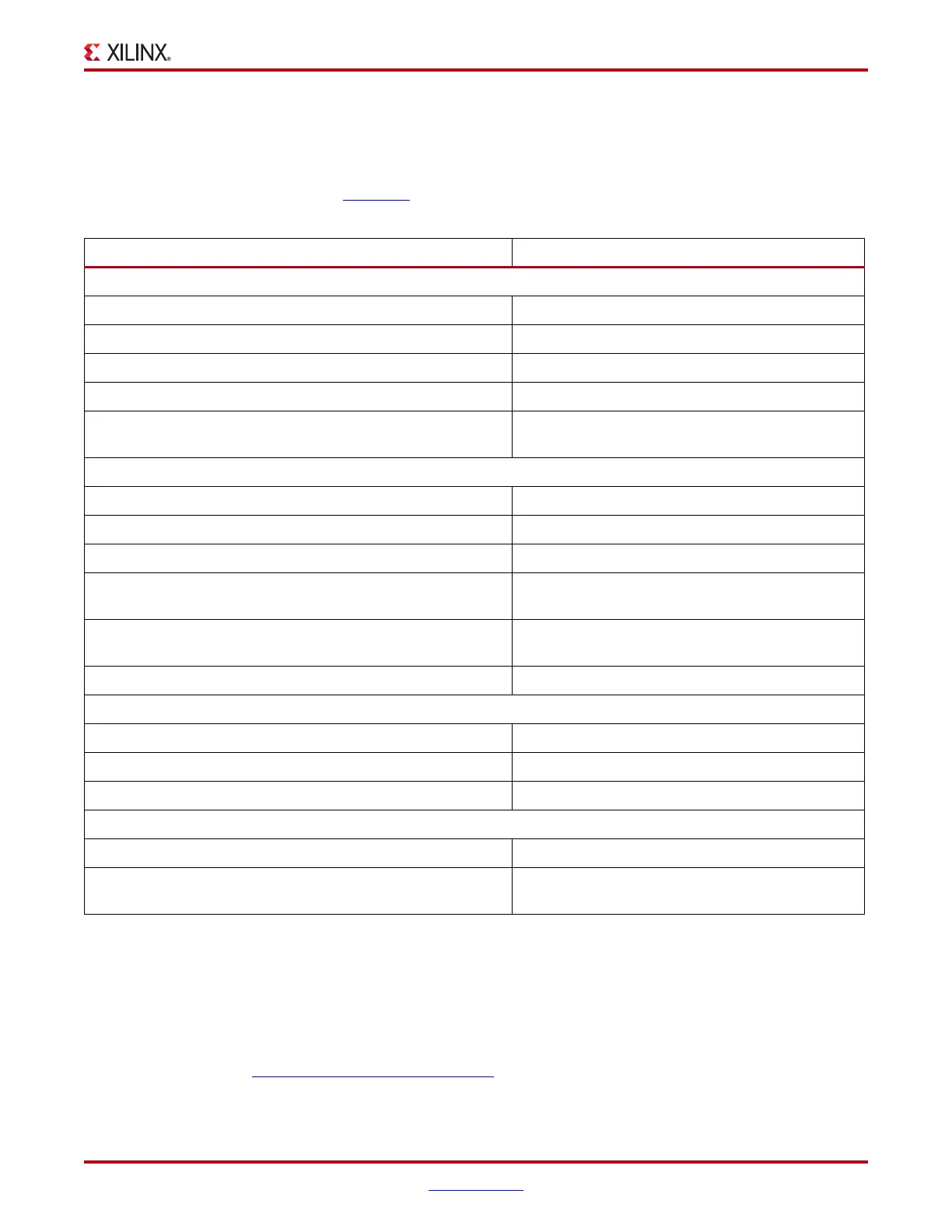

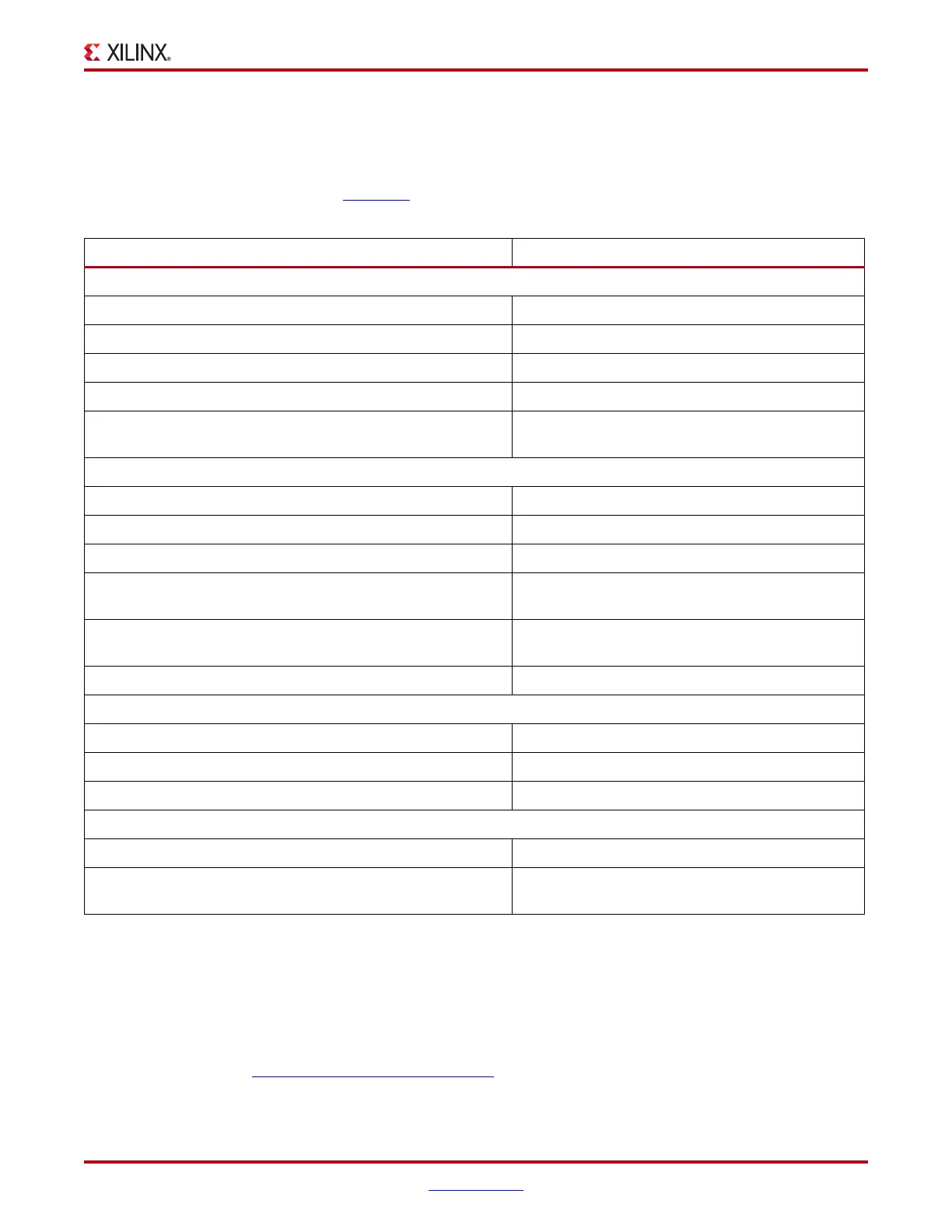

Table 2: Design Checklist

Parameter Description

General

Developer Name Xilinx

Target devices (stepping level, ES, production, speed grades) XC6VLX240T-1-FF1156

Source code provided Y (for custom logic only)

Source code format Verilog

Design uses code or IP from an existing reference design or

application note, third party, CORE G e nerator s o ftware

Uses code from a third party and LogiCORE IP from

the CORE Generator software

Simulation

Functional simulation performed Y

Timing simulation performed N

Testbench used for functional and timing simulations Y (for functional simulations)

Testbench format System Verilog (inhouse verification), Verilog

(customer deliverable)

Simulator software/version used ModelSim Questa 6.5a (inhouse verification)/

ModelSim 6.4b (out-of-box simulation support)

SPICE/IBIS simulations N

Implementation

Synthesis software tools/version used XST

Implementation software tools/versions used ISE Design Suite

Static timing analysis performed Y

Hardware Verification

Hardware verified Y

Hardware platform used for verification ML605 board and FMC X104 Connectivity daughter

card

Loading...

Loading...