ZCU104 Board User Guide 33

UG1267 (v1.1) October 9, 2018 www.xilinx.com

Chapter 3: Board Component Descriptions

The ZCU104 board PL DDR4 SODIMM interface adheres to the constraints guidelines

documented in the “PCB Guidelines for DDR4” section of UltraScale Architecture PCB Design

User Guide (UG583) [Ref 4]. The PL DDR4 SODIMM interface is a 40Ω impedance

implementation. Other memory interface details are also available in the UltraScale

Architecture FPGAs Memory Interface Solutions Product Guide (PG150) [Ref 5].

PSMIO

Table 3-5 provides PS MIO peripheral mapping implemented on the ZCU104 board. See the

Zynq UltraScale+ MPSoC Technical Reference Manual (UG1085) [Ref 2] for more information

on PS MIO peripheral mapping.

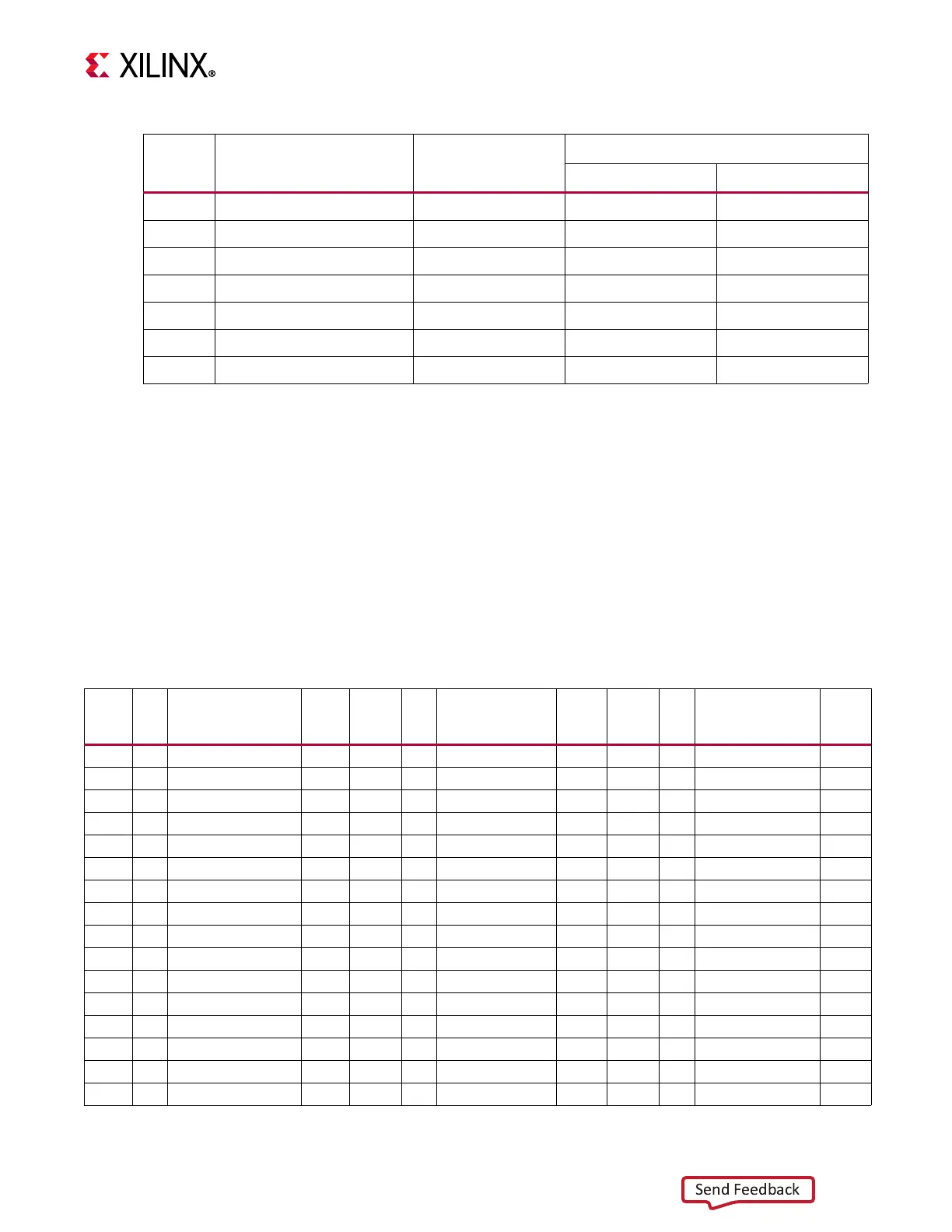

AC12 DDR4_SODIMM_WE_B SSTL12_DCI 151 WE_N/A14

AD14 DDR4_SODIMM_ACT_B SSTL12_DCI 114 ACT_N

AF13 DDR4_SODIMM_ALERT_B SSTL12_DCI 116 ALERT_N

AC13 DDR4_SODIMM_PARITY SSTL12_DCI 143 PARITY

AD12 DDR4_SODIMM_CS0_B SSTL12_DCI 149 CS0_N

AM13 DDR4_SODIMM_CS1_B SSTL12_DCI 157 CS1_N

AF12 DDR4_SODIMM_RESET_B LVCMOS12 108 RESET_N

Table 3-4: DDR4 SODIMM Socket J1 Connections to FPGA PL Banks 64, 65, and 66 (Cont’d)

XCZU7EV

(U1) Pin

Net Name I/O Standard

DDR4 SODIMM Memory J1

Pin Number Pin Name

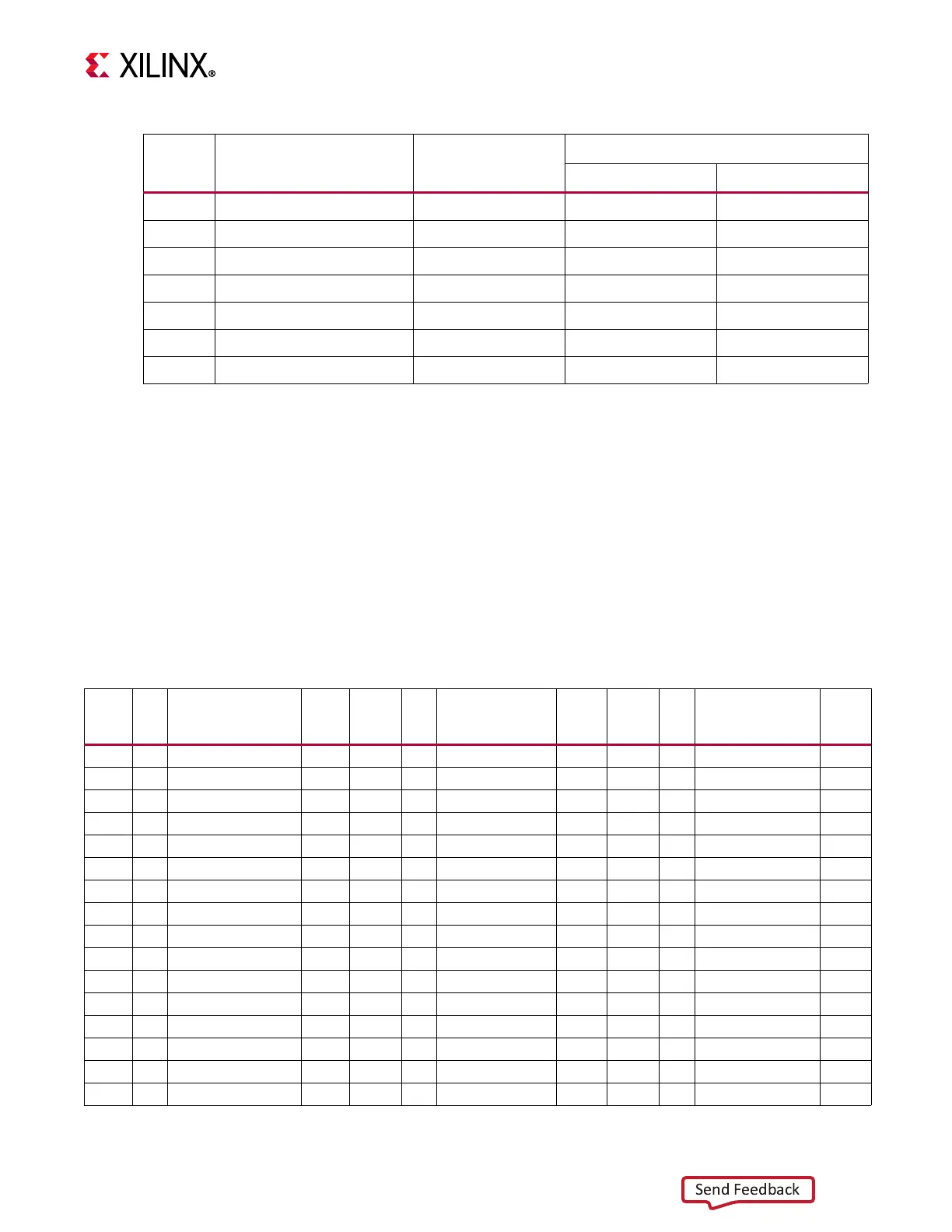

Table 3-5: MIO Connections

MIO

[25:0]

Bank 500

ZU7EV

U1

Pin

No.

Schematic Net Name Type

MI

[51:26]

Bank

501

ZU7EV

U1

Pin

No.

Schematic Net Name Type

MIO

[77:52]

Bank 502

ZU7EV

U1

Pin

No.

Schematic Net Name Type

MIO25 D29 MIO25_CAN_RX CAN MIO51 F34 MIO51_SDIO_CLK_R SD1 MIO77 L34 MIO77_ENET_MDIO MDIO3

MIO24 E28 MIO24_CAN_TX CAN MIO50 F33 MIO50_SDIO_CMD_R SD1 MIO76 L33 MIO76_ENET_MDC MDIO3

M I O 23 B 2 9 N o t C o n ne c t e d N C M I O 4 9 F 3 2 M I O4 9 _ S D I O_ D A T 3 _ R S D 1 M I O 7 5 L 3 0 M I O7 5 _ E N E T_ R X _ C TR L G E M3

M I O 22 F2 8 N o t C o n n e ct e d N C M I O4 8 F 3 1 M I O 4 8 _ S DI O _ D A T 2_ R S D 1 M I O 74 L 29 M I O7 4 _ E N E T_ R X _ D 3 G E M 3

MIO21 C28 UAR T1_TXD_MIO21_RXD UART1 MIO47 F30 MIO4 7_SDIO_DAT1_R SD1 MIO73 K34 M IO73_ENET_RX_D 2 GEM3

MIO20 E29 UART1_RXD_M IO20_TXD UART1 MIO46 E34 MIO46_SDIO_DAT 0_R SD1 MIO72 K33 MIO72_ENET_RX_D 1 GEM3

MIO19 B28 UART0_RXD_MIO19_TXD UART0 MIO45 E33 MIO45_SDIO_DETECT SD1 MIO71 K32 MIO71_ENET _RX_D0 GEM3

MIO18 F27 UART0_TXD_MIO18_RXD UART0 MIO44 E32 Not Connected NC MIO70 K31 MIO70_ENET_RX_CLK GEM3

MIO17 C29 MIO17_I2C1_SDA I2C1 MIO43 E30 Not Connected NC MIO69 K30 MIO69_ENET_TX_CTRL GEM3

MIO16 A28 MIO16_I2C1_SCL I2C1 MIO42 D34 Not Connected NC MIO68 K29 MIO68_ENET_TX_D3 GEM3

M I O 15 E 2 7 No t C o n n ec t e d N C M I O 4 1 D 3 2 N o t C o n n e c t ed N C M I O 67 K 28 M I O6 7 _ E N E T_ T X _ D 2 G E M 3

M I O 14 A 2 7 N o t Co n n e c t ed N C M I O 4 0 D 3 1 N o t C o n n e c te d N C M I O6 6 J 3 4 M IO 6 6 _ E N ET _ T X _ D1 G E M3

M I O 13 D 2 7 N o t Co n n e c t e d N C M I O 3 9 D 3 0 N o t C o n n e c te d N C M I O 65 J3 2 M I O6 5 _ E N E T_ T X _ D 0 G E M 3

M I O 12 C 2 7 N o t C o nn e c t e d N C M I O 3 8 C 3 4 N o t C o n ne c t e d N C M I O 6 4 J 3 1 M I O 6 4 _ EN E T _ T X _C L K G E M3

M I O 11 B 2 6 N o t C o n ne c t e d N C M I O 3 7 C3 3 N o t C o n n ec t e d N C M I O 6 3 J 3 0 M I O 6 3_ U S B _ D AT A 7 _ R U S B0

M I O 10 F2 6 N o t C o n n e ct e d N C M I O3 6 C 3 2 N o t C o n n e ct e d N C M I O 6 2 J 2 9 M I O 6 2_ U S B _ D AT A 6 _ R U S B0

Loading...

Loading...