RFSoC Data Converter Evaluation Tool User Guide 35

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 4: Clocking

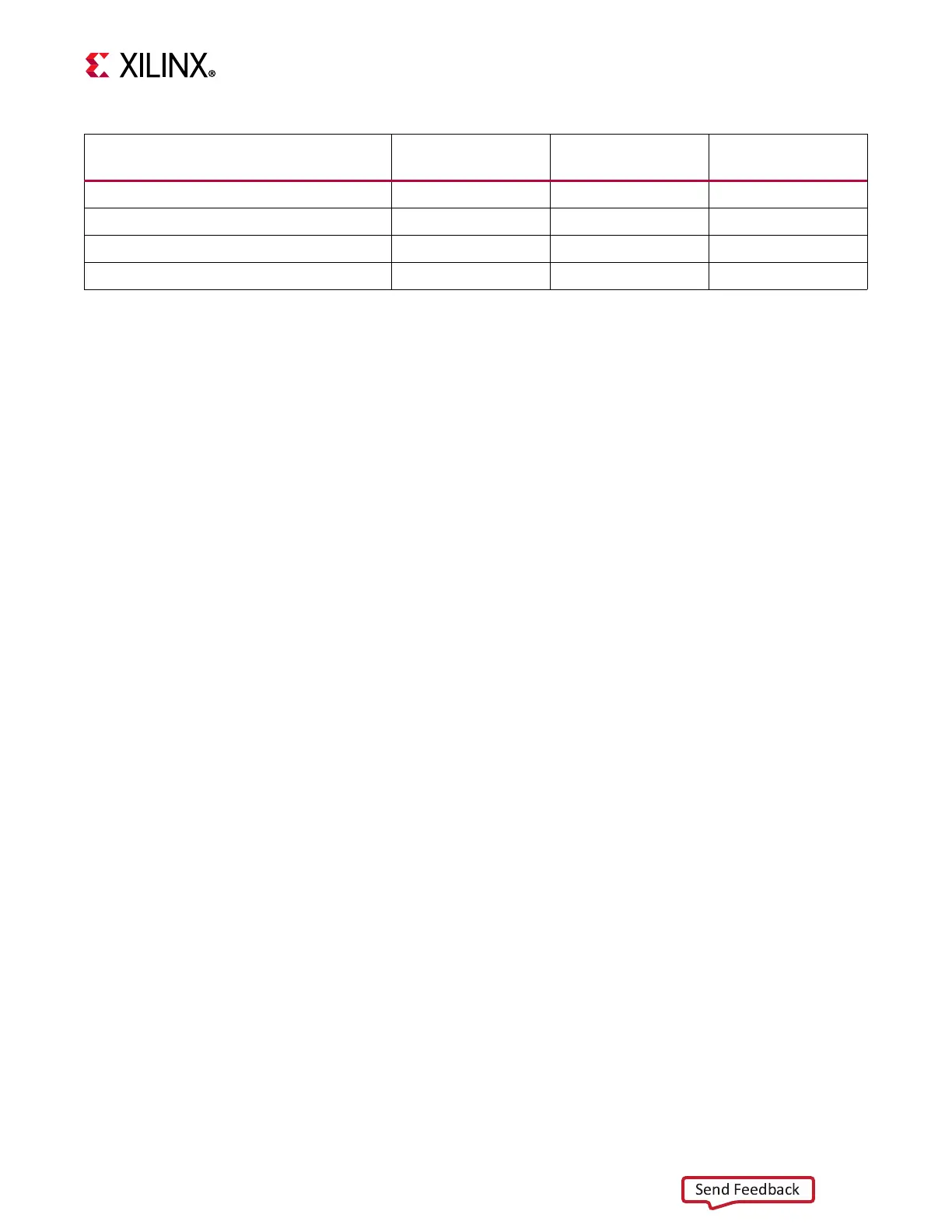

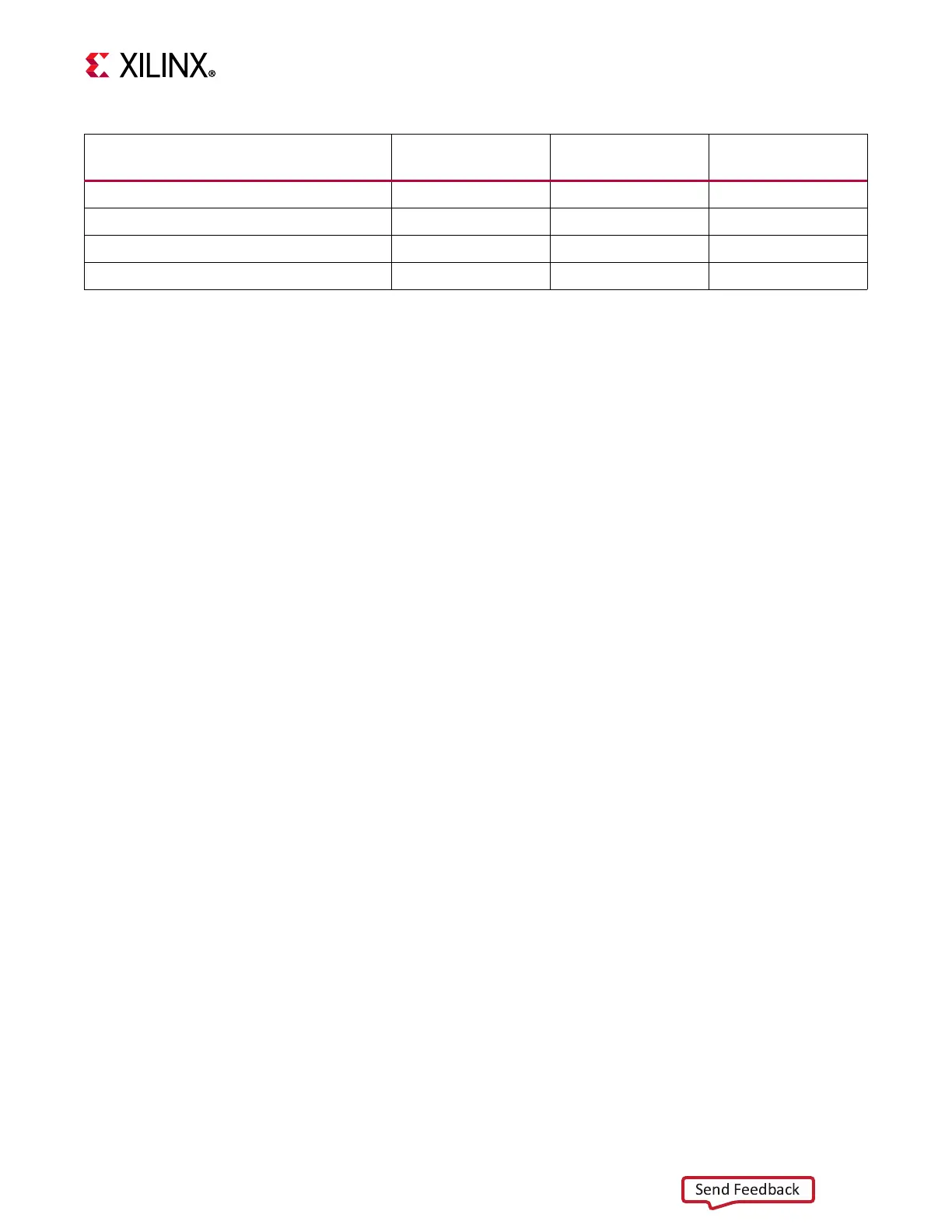

DAC 4 block- output AXIS data FIFOs x (dac reset_4_n)

DAC 5 block- output AXIS data FIFOs x (dac reset_5_n)

DAC 6 block- output AXIS data FIFOs x (dac reset_6_n)

DAC 7 block- output AXIS data FIFOs x (dac reset_7_n)

Table 4-3: Reset Distribution in the Evaluation Tool Design (Cont’d)

Logic Block pl_resetn0 ddr4_sync_rst

User-controlled

Reset Block

Loading...

Loading...