6–10 Chapter 6: Board Test System

Using the Board Test System

Cyclone V SoC Development Kit May 2013 Altera Corporation

User Guide

Pattern Generator

This control specifies the test pattern to output to the monitor. The following choices

are available:

Pattern

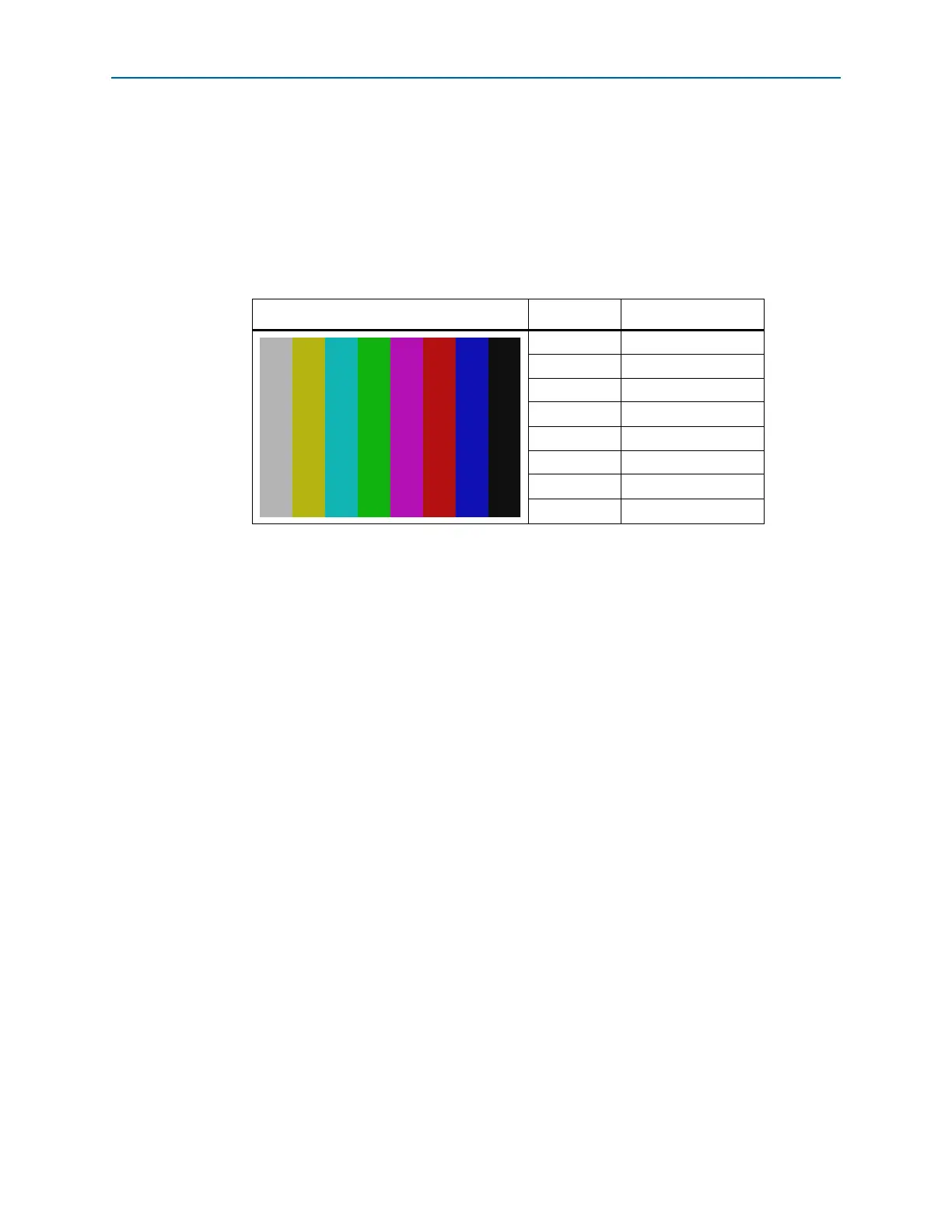

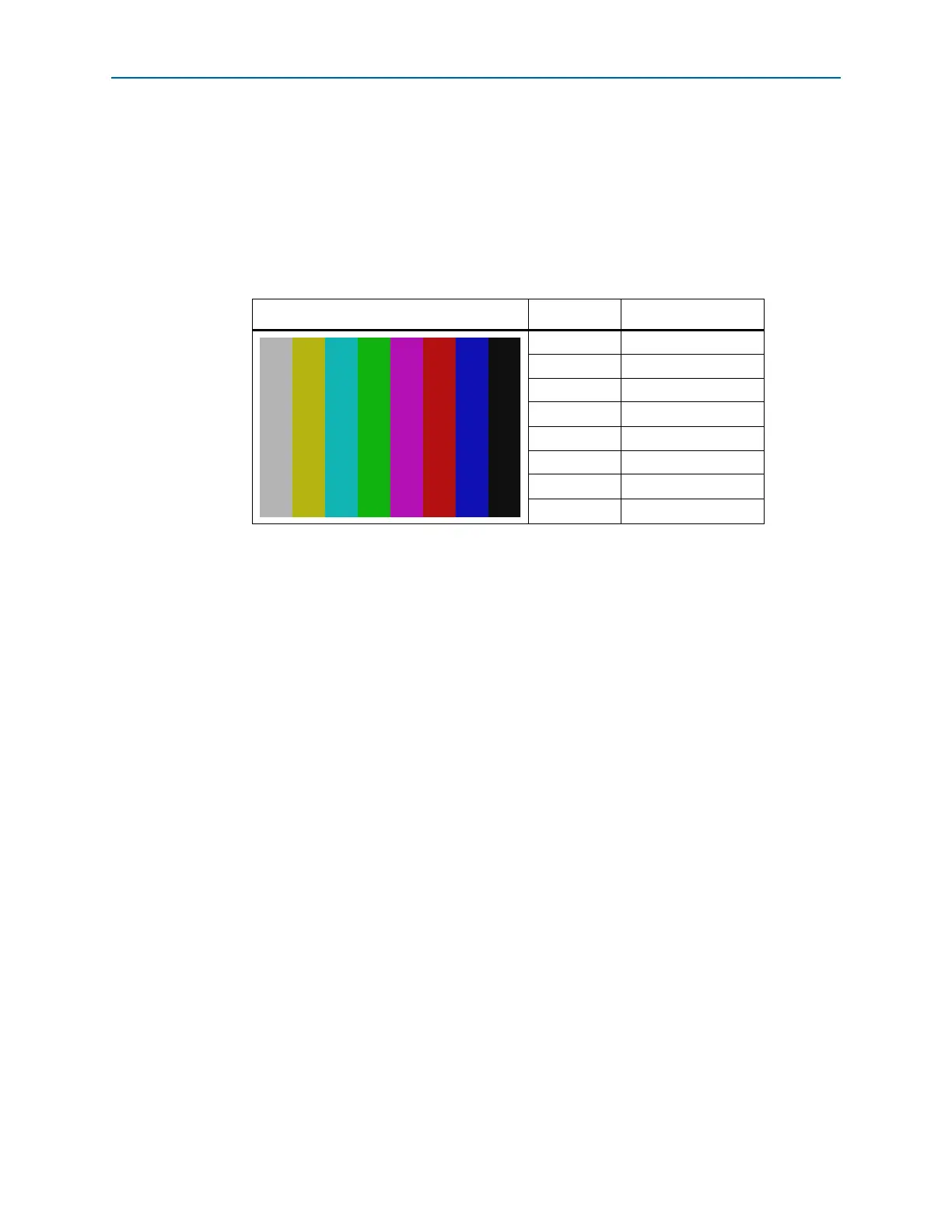

■ Color bar—Specifies a video color bar pattern with eight vertical color bars as

shown in table Table 6–1.

■ Pathological—Specifies a video color bar pattern with two horizontal color bars

that stresses the receive PLL.

■ PRBS—Specifies a pseudo-random bit sequence useful for electrical testing of the

interface for data integrity.

Intensity

Specifies the color intensity of the transmitted color bar pattern. The following choices

are available.

■ 75%—Specifies 75% intensity.

■ 100%—Specifies 100% intensity.

SDI Standard

Specifies the video standard used by the pattern generator on the SDI video stream.

The following choices are available:

■ SD—Specifies a 270 Mbps data rate.

■ HD—Specifies a 1.485 Gbps data rate.

■ 3G HD—Specifies a 2.97 Gbps data rate.

Clock Source

Specifies the clock used by the SDI PLL to lock onto. The following choices are

available:

■ Lock to host—Locks the SDI PLL to the local reference on the Cyclone V SoC

Development board.

■ Lock to input—Locks the SDI PLL to the SDI video data input.

Table 6–1. HDMI Color Bar Test Pattern

Color Bars Color RGB Values

White/Grey 180,180,180

Yellow 180,180,16

Cyan 16,180,180

Green 16,180,16

Magenta 180,16,180

Red 180,16,16

Blue 16,16,180

Black 16,16,16

Loading...

Loading...