Preliminary Technical Data UG-1828

Rev. PrC | Page 169 of 338

The power measurement block has a dynamic range of 60dB. Signals lower than −60 dBFS may not be measured accurately. The power

masurement could be read through the API function adi_adrv9001_Rx_DecimatedPower_Get().

Detector Overload and QEC

If the device is operating in AGC mode, when an overload is detected, the Rx QEC calibration will be frozen. AGC will be able to adjust

the Rx Gain Index to attempt to bring the received signal to a level that is under the overload threshold so that input signal no longer

triggers the overload detector. Then Rx QEC calibration will resume.

If the device is operating in MGC mode, when an overload is detected, the Rx QEC calibration will be frozen as well. However since the

device is operating in MGC mode, if input signal remains a high level above the overload threshold, then Rx QEC will remain frozen and

will not recover until the input signal is below the overload threshold.

AGC CLOCK AND GAIN BLOCK TIMING

The AGC clock is the clock which drives the AGC state machine. In ADRV9001 device, the default AGC clock (to support a set of

standard sample rates) is at 184.32 MHz. When arbitrary sample rate is adopted in Rx, the AGC clock could vary.

The AGC state machine contains 3 states: Gain Update Counter, followed by the Slow Loop Settling (SLS) Delay, and 5 AGC clock cycles

delay. The total time between gain updates (gain update period) is a combination of slowLoopSettlingDelay and 5 AGC clock cycles.

(Note the first slowLoopSettlingDelay in grey is a part of Gain Update Counter.)

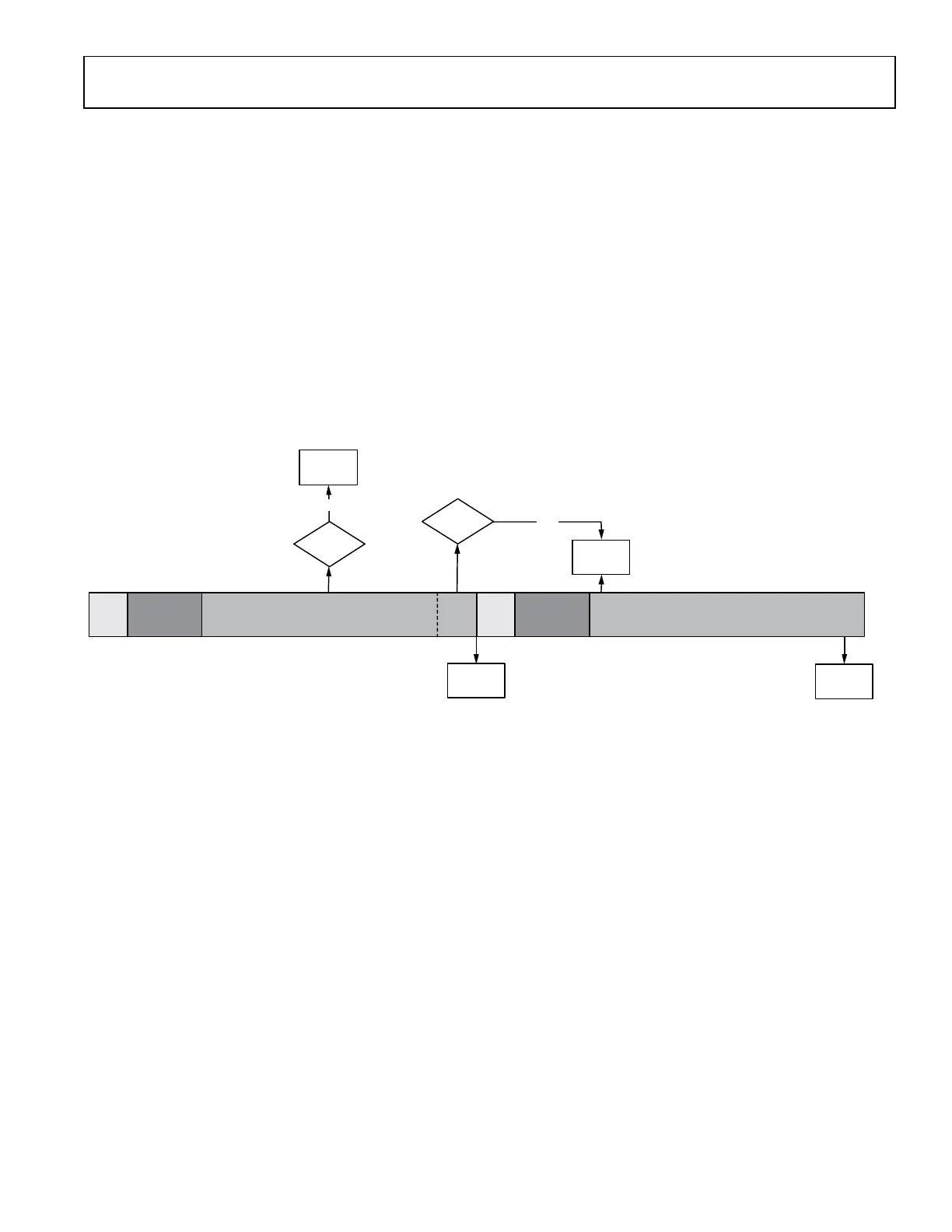

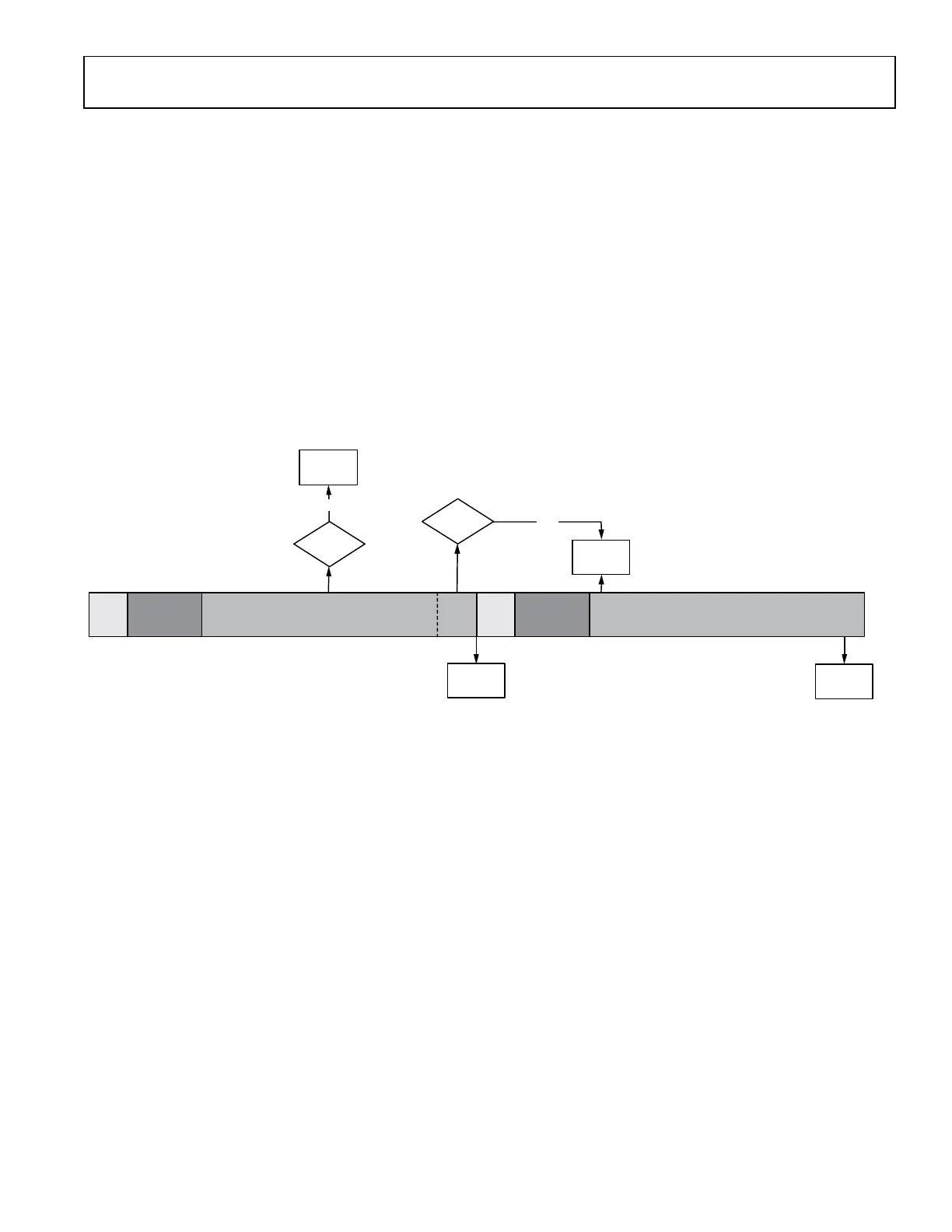

Figure 158. Delayed Gain Attack for Nondelayed Gain Recovery

Figure 158 outlines the operation of the AGC state machine. The diagram outlines possible gain change scenarios rather than a practical

example of AGC operation. The possible gain change scenarios are described below:

• AGC Gain Attack within gain update counter, but more than an SLS delay before the gain update counter expiry – Because slow loop

settling (SLS) is typically several orders of magnitude smaller than gain update counter, this is the most common gain decrement

scenario. This type of AGC Gain Attack is named as Gain Attack Type 1 as shown in Figure 158.

• AGC Gain Attack within gain update counter, but within a SLS delay before the gain update counter expiry – This is a special case,

which will rarely occur in applications per the reasoning in 1). This type of AGC Gain Attack is named as Gain Attack Type 2 as

shown in Figure 158.

• AGC Gain Recovery at the end of the gain update counter – Note that when fast recovery is enabled, the gain update counter is

substituted with the low under range interval. A gain attack may occur within the gain update counter when fast attack is enabled. A

gain recovery event may only occur at the end of gain update counter (or low under range interval in “fast recovery” mode) as

previously discussed. This is mainly for aligning the gain recovery (for desired signal) with the frame or subframe boundary. After a

gain attack, a gain change counter with a value equal to the SLS delay is started. No further gain attacks are allowed while this

counter is running. This allows the minimum time to be set between gain changes.

However the gain change counter also prevents the AGC from moving from the gain update counter state to the slow loop settling delay

state since it must wait until the expiry of the SLS delay. Therefore if a gain attack occurred very close to end of the gain update counter

state, the gain change counter would delay the start of the SLS state and shift the gain recovery event as shown in Figure 158. Whereas in

Figure 159, gain recovery event is always aligned with the vertical dash lines.

GAIN UPDATE COUNTER

5 AGC

CLOCK

CYCLE

IMMEDIATE

GAIN

ATTACK

GAIN

ATTACK

TYPE 1

SLOW

LOOP

SETTLING

DELAY

SLOW

LOOP

SETTLING

DELAY

SLOW

LOOP

SETTLING

DELAY

5 AGC

CLOCK

CYCLE

GAIN UPDATE COUNTER

GAIN

ATTACK

TYPE 2

YES

GAIN

RECOVERY

DELAYED

GAIN

RECOVERY

GAIN

RECOVERY

YES

24159-

116

Loading...

Loading...