UG-1828 Preliminary Technical Data

Rev. PrC | Page 64 of 338

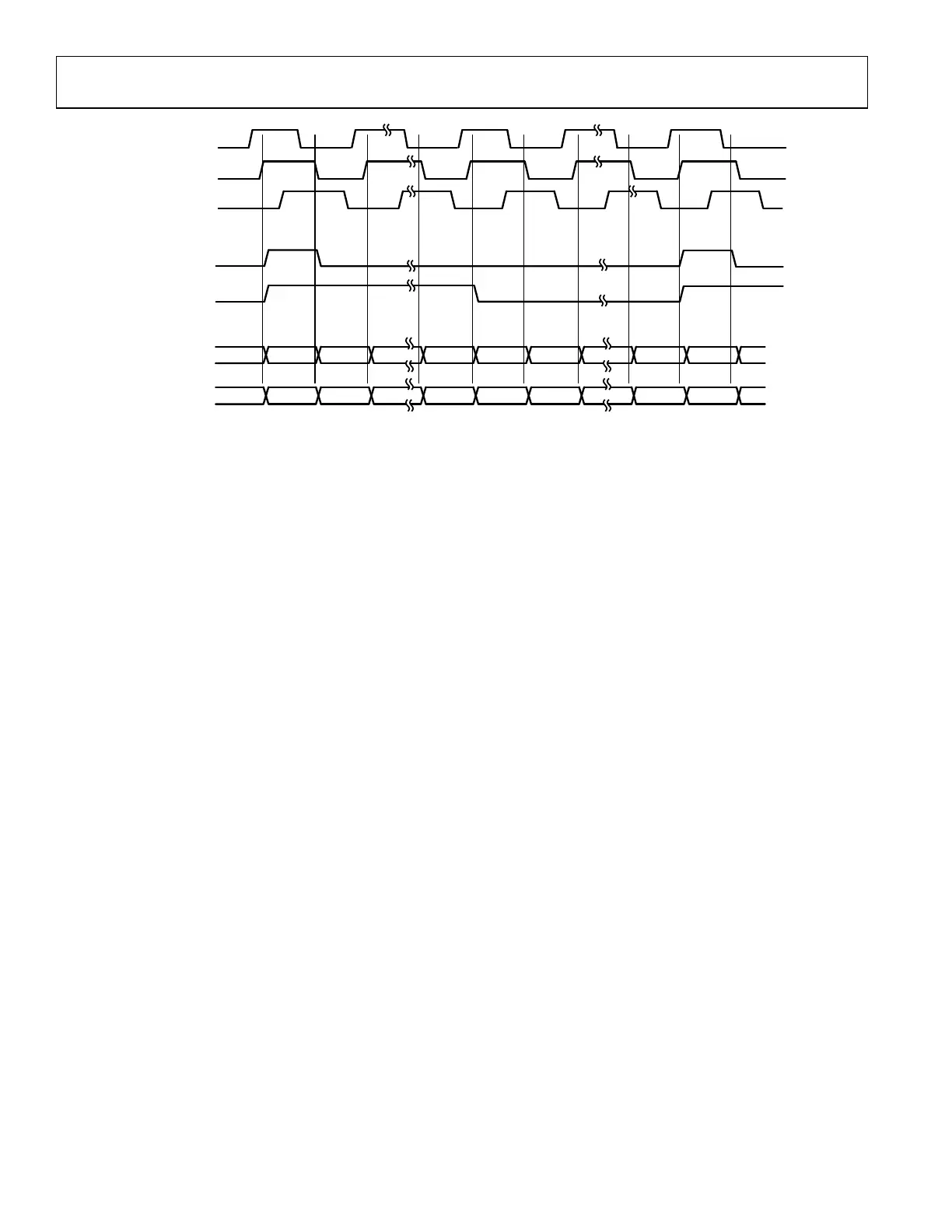

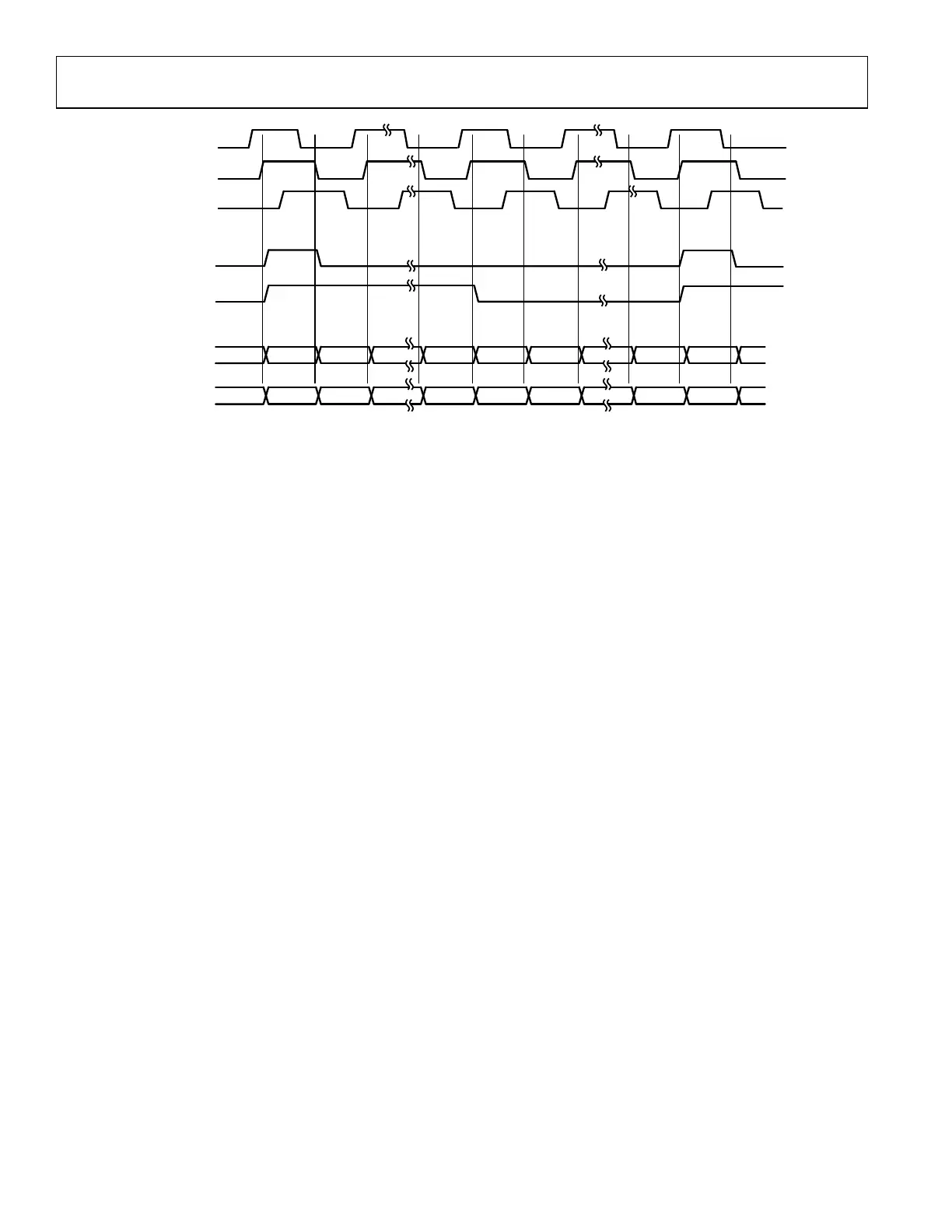

Figure 53. Transmit LSSI Timing for 16-Bit I/Q Data Sample Sharing One Lane

Receive LSSI Interface with 2×, 4×, and 8× Data Clock Rates

ADRV9001 receive LSSI supports the 2 times, 4 times, or 8 times of the data clock rate for some applications, which is similar with the

Receiver CSSI mode, refer the timing diagrams in Receive CSSI Interface with 2×, 4×, and 8× Data Clock Rates.

ENHANCED RX SSI MODE

The Rx SSI LVDS two lane and CMOS one lane mode have two enhanced modes to support 22bit data samples and 15 bit data samples in

I/Q mode.

In 22bit data samples case, the 32 bit interface data bus has the following fields:

• 22bits of data sample (I/Q from Rx Data path: unrounded data samples: RxDataPathI/Q[21:0])

• 1bit = 0 (Constant)

• 1bit Gain Change ( Slicer or Index Gain Change flag )

• 8bits Gain (Slicer or Index Gain )

which produce the following Interface data with 32bit data format for the CMOS and LVDS SSI:

• LVDS 32bit: 2 lanes (I & Q) of 32 bit each

o LSSI_DATA_I/Q [31:0] = {RxDataPathI/Q[21:0], b0, Gain_Change, Gain [7:0]}

• CMOS 64bit: 1 Lane (I & Q)

o CSSI_DATA [63:0] = {RxDataPathI[21:0] , b0, Gain_Change, Gain[7:0],

RxDataPathQ[21:0] , b0, Gain_Change, Gain[7:0] }

In 15bit data samples case, the 16bit interface data bus has the following fields:

• 15bits of data sample (15 bit I/Q rounded from 22 bit Rx Data path samples)

• 1bit Gain Change ( Slicer or Index Gain Change flag )

which produce the following Interface data with 16 bit data format for the CMOS and LVDS SSI:

• LVDS 16bit: 2 lanes (I & Q) of 16 bit each

o LSSI_DATA_I/Q [15:0] = {RxDataPathI/Q[21:0], b0, Gain_Change, Gain [7:0]}

• CMOS 32bit: 1 Lane (I & Q)

o CSSI_DATA [31:0] = {RxDataPathI rounded[14:0] , Gain_Change, RxDataPathQ rounded[14:0], Gain_Change }

Some of the other basic configuration modes, such as MSB/LSB first option, I or Q first option (for CMOS 1 lane), Long/Short strobe

option are similar to previous SSI LVDS/CMOS 16bit operation.

TX_IDATA_IN+/–

TX_DCLK_IN+

OR

TX_DCLK_IN+

TX_DCLK_OUT+

TX_STROBE_IN+

OR

TX_STROBE_IN+

I0_D15

TX_QDATA_IN+/–

I0_D0 Q0_D15 Q0_D14 I0_Q0 I1_D15I0_D14

24159-050

Loading...

Loading...