UG-1828 Preliminary Technical Data

Rev. PrC | Page 80 of 338

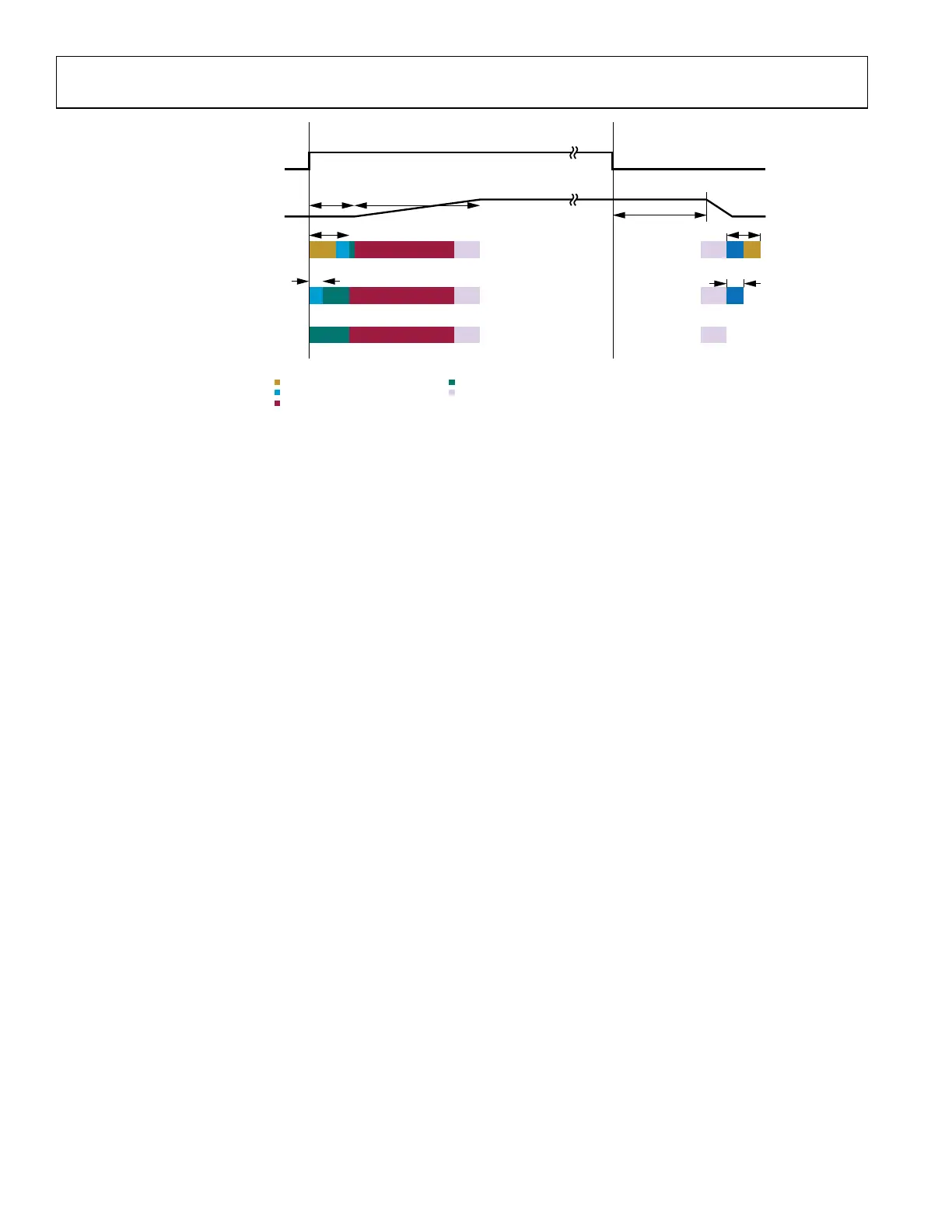

Figure 73. Channel Power-Up and Power-Down Sequence in Different Power Savings Modes (PLL Retune @ Frame Boundary Case)

In this case, in all power saving modes, the PLL tuning is performed during enableSetupDelay instead of enableRiseToAnalogOnDelay.

Therefore, enableSetupDelay is much longer as it must allow time to tune the PLL. This means that the additional power up durations

t

PowerUpPSM

are much shorter and thus higher power savings can be achieved while setting the enableRiseToAnalogOnDelay to a much

smaller value.

All above description is for internal LOs scenarios, if ADRV9001 is configured with external LO mode, users take the responsibility to

configure or re-tune the external PLLs, ADRV9001 channel power up and power down sequence in different power saving modes are

same with Figure 71, users should make sure the external LOs are ready before the enableRiseToAnalogOnDelay is expiry.

Impact of Power Savings on Timing Parameter Selection

As explained in the previous section, certain power savings modes cannot be entered if the enableRiseToAnalogOnDelay for that channel

is not greater than the duration of the additional power up procedures needed in that mode.

For transmit channels, if the propagation delay is quite large, the enableRiseToAnalogOnDelay chosen may already be larger than the

longest power up procedure duration, that is, t

PowerUpPSM2

. In this case, there is no impact to the selection of the timing parameters.

For receive channels, or transmit channels with short propagation delays, the enableRiseToAnalogOnDelay must be chosen larger than

t

PowerUpPSM1

to enter Power Savings Mode 1 and larger than t

PowerUpPSM2

to enter Power Savings Mode 2 and higher. The

enableRiseToOnDelay, if it is being used, must also increase as it must always be larger than enableRiseToAnalogOnDelay. However, none

of the other timing parameters are affected by the power savings mode.

At the end of the frame, the power-down procedures take some small but finite time. For receiver channels with large propagation delay,

this may have no impact because the digital datapath might be on for a long time after the analog has powered down.

For transmit channels or receive channels with short propagation delays, the minimum period between the channel enable falling edge

and the next rising edge must be enableHoldDelay plus the additional time needed for the extra power down procedures (t

PowerUpPSM1

,

t

PowerUpPSM2

). This prevents PLL or LDO from beginning power up in the new frame even before it has finished powering down in the old

one.

Hardware and Software Restrictions for Timing Parameters

As previously mentioned, the bounds provided for each of these timing parameters and the guard times between rising and falling edges

of the receiver and transmitter enable signals are only guidelines. There are almost no hardware or software restrictions preventing users

from setting these parameters anyway they like including harmful or useless ways. There are in place a few restrictions, however, which

are outlined as follows:

• All timing parameters that must be provided by user have to be within the range of 0 ms to 91 ms. These bounds are specified,

assuming the delay generation blocks run at 184.32 MHz (system clock). If operating at a different frequency, the maximum bound

scales accordingly. For example, if using a 160 MHz clock, the max delay is 91 ms/184.32 × 160 = 79 ms).

• For all channels the enableRiseToOnDelay must be greater than or equal to the enableRiseToAnalogOnDelay, provided the

enableRiseToOnDelay parameter is being used, that is, ADRV9001 is controlling antenna switch and/or LNA power.

• For transmitter channels, the enableHoldDelay must be less than or equal to the enableFallToOffDelay.

• For receiver channels, the enableFallToOffDelay must be less than or equal to the enableHoldDelay.

PIN: CH_ENABLE

CH ANALOG

POWER SAVINGS MODE 2

POWER SAVINGS MODE 1

POWER SAVINGS MODE 0

LDO POWER UP / DOWN

PLL POWER UP / DOWN

PLL TUNING

t

PowerUpPSM2

t

PowerDnPSM2

t

PowerDnPSM1

t

chEnaRise2AnaOn

t

chEnaFall2Off

IDLE

Tx CHANNEL ANALOG POWER UP / DOWN

t

PowerUpPSM1

t

chEnaSetup

24159-065

Loading...

Loading...