87

AT90S2313

0839G–08/01

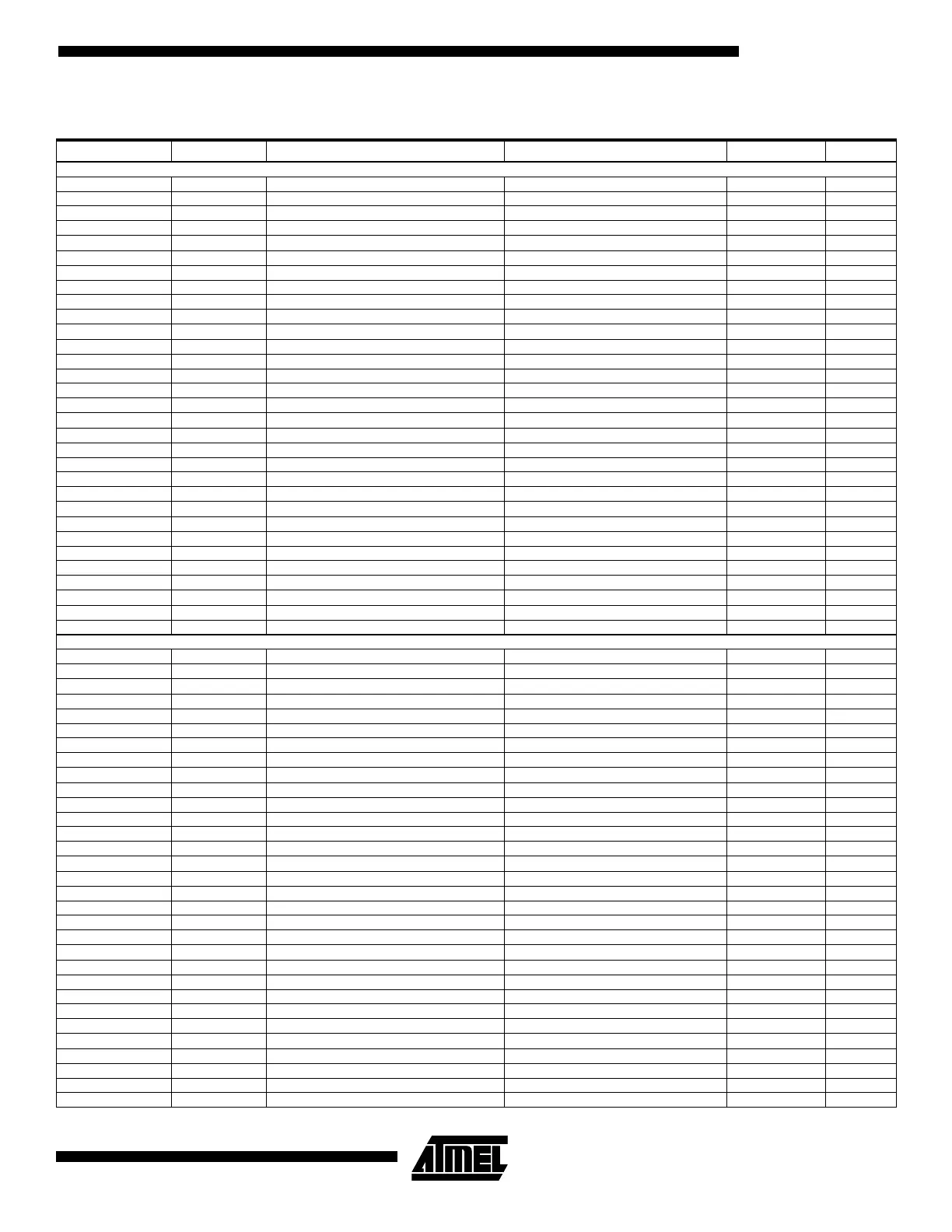

DATA TRANSFER INSTRUCTIONS

MOV Rd, Rr Move between Registers Rd

← Rr None 1

LDI Rd, K Load Immediate Rd

← KNone1

LD Rd, X Load Indirect Rd

← (X) None 2

LD Rd, X+ Load Indirect and Post-Inc. Rd

← (X), X ← X + 1 None 2

LD Rd, -X Load Indirect and Pre-Dec. X

← X − 1, Rd ← (X) None 2

LD Rd, Y Load Indirect Rd

← (Y) None 2

LD Rd, Y+ Load Indirect and Post-Inc. Rd

← (Y), Y ← Y + 1 None 2

LD Rd, -Y Load Indirect and Pre-Dec. Y

← Y − 1, Rd ← (Y) None 2

LDD Rd, Y+q Load Indirect with Displacement Rd

← (Y + q) None 2

LD Rd, Z Load Indirect Rd

← (Z) None 2

LD Rd, Z+ Load Indirect and Post-Inc. Rd

← (Z), Z ← Z+1 None 2

LD Rd, -Z Load Indirect and Pre-Dec. Z

← Z - 1, Rd ← (Z) None 2

LDD Rd, Z+q Load Indirect with Displacement Rd

← (Z + q) None 2

LDS Rd, k Load Direct from SRAM Rd

← (k) None 2

ST X, Rr Store Indirect (X)

← Rr None 2

ST X+, Rr Store Indirect and Post-Inc. (X)

← Rr, X ← X + 1 None 2

ST -X, Rr Store Indirect and Pre-Dec. X

← X - 1, (X) ← Rr None 2

ST Y, Rr Store Indirect (Y)

← Rr None 2

ST Y+, Rr Store Indirect and Post-Inc. (Y)

← Rr, Y ← Y + 1 None 2

ST -Y, Rr Store Indirect and Pre-Dec. Y

← Y - 1, (Y) ← Rr None 2

STD Y+q, Rr Store Indirect with Displacement (Y + q)

← Rr None 2

ST Z, Rr Store Indirect (Z)

← Rr None 2

ST Z+, Rr Store Indirect and Post-Inc. (Z)

← Rr, Z ← Z + 1 None 2

ST -Z, Rr Store Indirect and Pre-Dec. Z

← Z - 1, (Z) ← Rr None 2

STD Z+q, Rr Store Indirect with Displacement (Z + q)

← Rr None 2

STS k, Rr Store Direct to SRAM (k)

← Rr None 2

LPM Load Program Memory R0

← (Z) None 3

IN Rd, P In Port Rd

← PNone1

OUT P, Rr Out Port P

← Rr None 1

PUSH Rr Push Register on Stack STACK

← Rr None 2

POP Rd Pop Register from Stack Rd

← STACK None 2

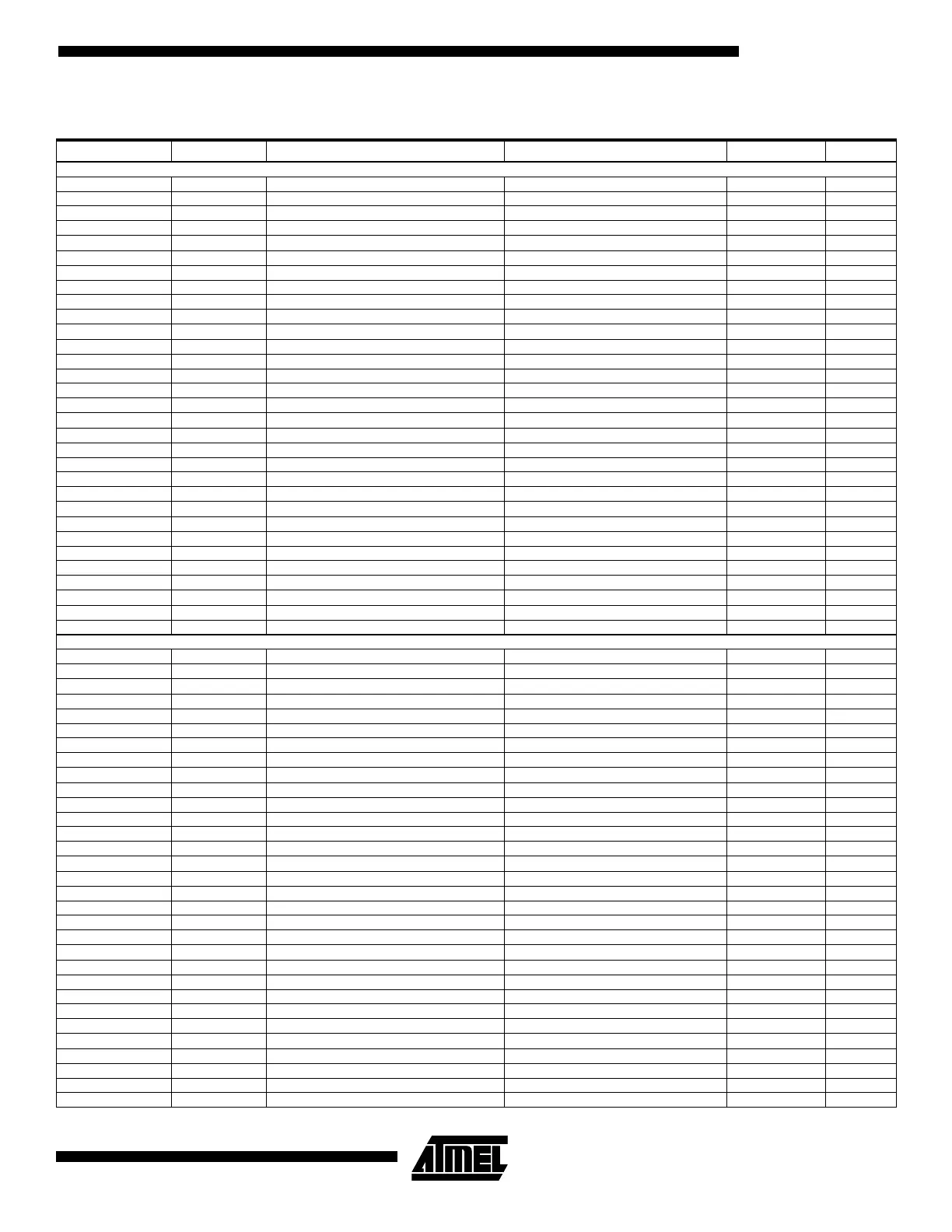

BIT AND BIT-TEST INSTRUCTIONS

SBI P, b Set Bit in I/O Register I/O(P,b)

← 1None2

CBI P, b Clear Bit in I/O Register I/O(P,b)

← 0None2

LSL Rd Logical Shift Left Rd(n+1)

← Rd(n), Rd(0) ← 0 Z,C,N,V 1

LSR Rd Logical Shift Right Rd(n)

← Rd(n+1), Rd(7) ← 0 Z,C,N,V 1

ROL Rd Rotate Left through Carry Rd(0)

←=C, Rd(n+1) ← Rd(n), C ←=Rd(7) Z,C,N,V 1

ROR Rd Rotate Right through Carry Rd(7)

←=C, Rd(n) ← Rd(n+1), C ←=Rd(0) Z,C,N,V 1

ASR Rd Arithmetic Shift Right Rd(n)

← Rd(n+1), n = 0..6 Z,C,N,V 1

SWAP Rd Swap Nibbles Rd(3..0)

←=Rd(7..4), Rd(7..4) ←=Rd(3..0) None 1

BSET s Flag Set SREG(s)

← 1 SREG(s) 1

BCLR s Flag Clear SREG(s)

← 0 SREG(s) 1

BST Rr, b Bit Store from Register to T T

← Rr(b) T 1

BLD Rd, b Bit Load from T to Register Rd(b)

← TNone1

SEC Set Carry C

← 1C1

CLC Clear Carry C

← 0C1

SEN Set Negative Flag N

← 1N1

CLN Clear Negative Flag N

← 0N1

SEZ Set Zero Flag Z

← 1Z1

CLZ Clear Zero Flag Z

← 0Z1

SEI Global Interrupt Enable I

← 1I1

CLI Global Interrupt Disable I

← 0I1

SES Set Signed Test Flag S

← 1S1

CLS Clear Signed Test Flag S

← 0S1

SEV Set Two’s Complement Overflow V

← 1V1

CLV Clear Two’s Complement Overflow V

← 0V1

SET Set T in SREG T

← 1T1

CLT Clear T in SREG T

← 0T1

SEH Set Half-carry Flag in SREG H

← 1H1

CLH Clear Half-carry Flag in SREG H

← 0H1

NOP No Operation None 1

SLEEP Sleep (see specific descr. for Sleep function) None 1

WDR Watchdog Reset (see specific descr. for WDR/timer) None 1

Instruction Set Summary (Continued)

Mnemonic Operands Description Operation Flags # Clocks

Loading...

Loading...