40

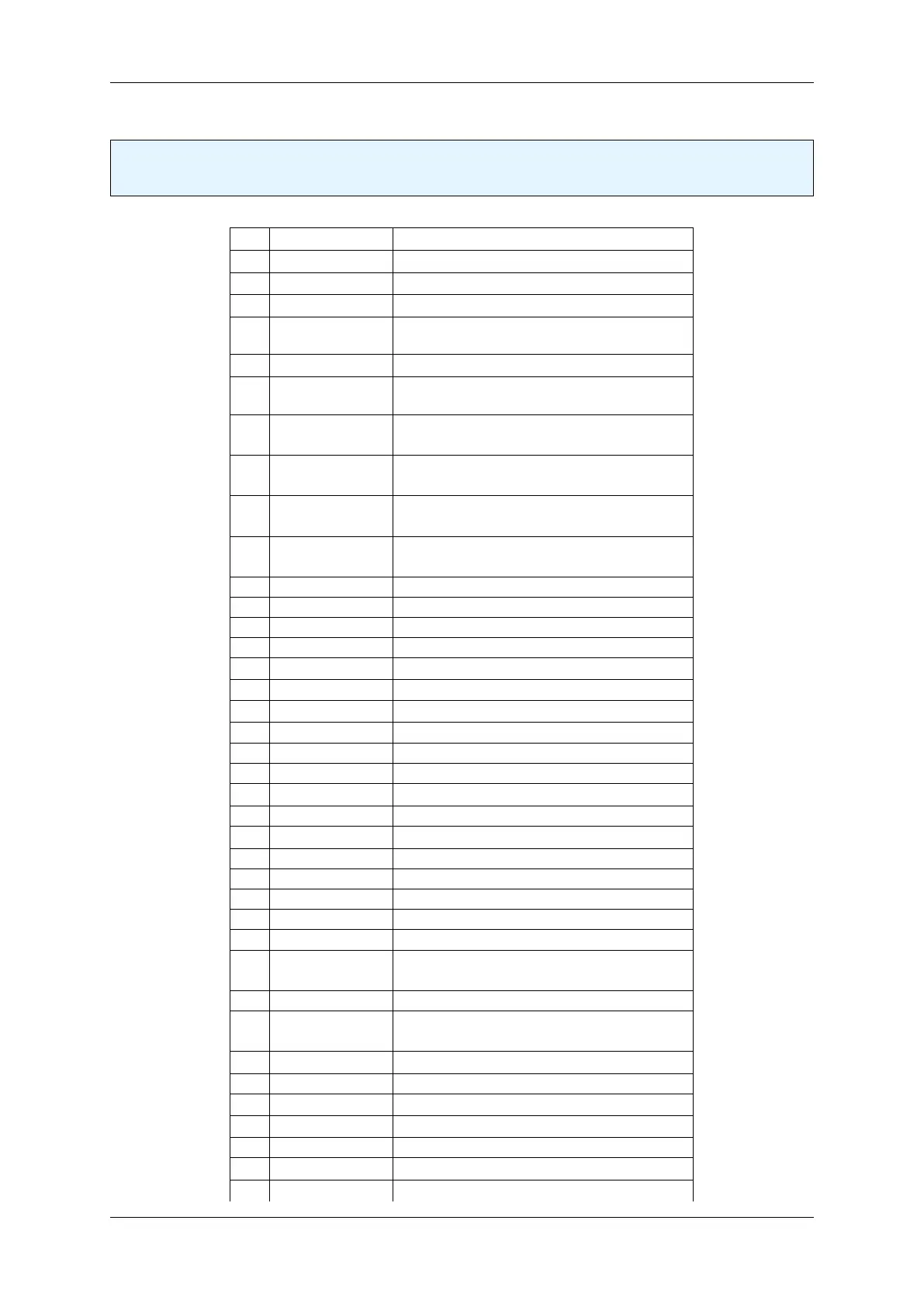

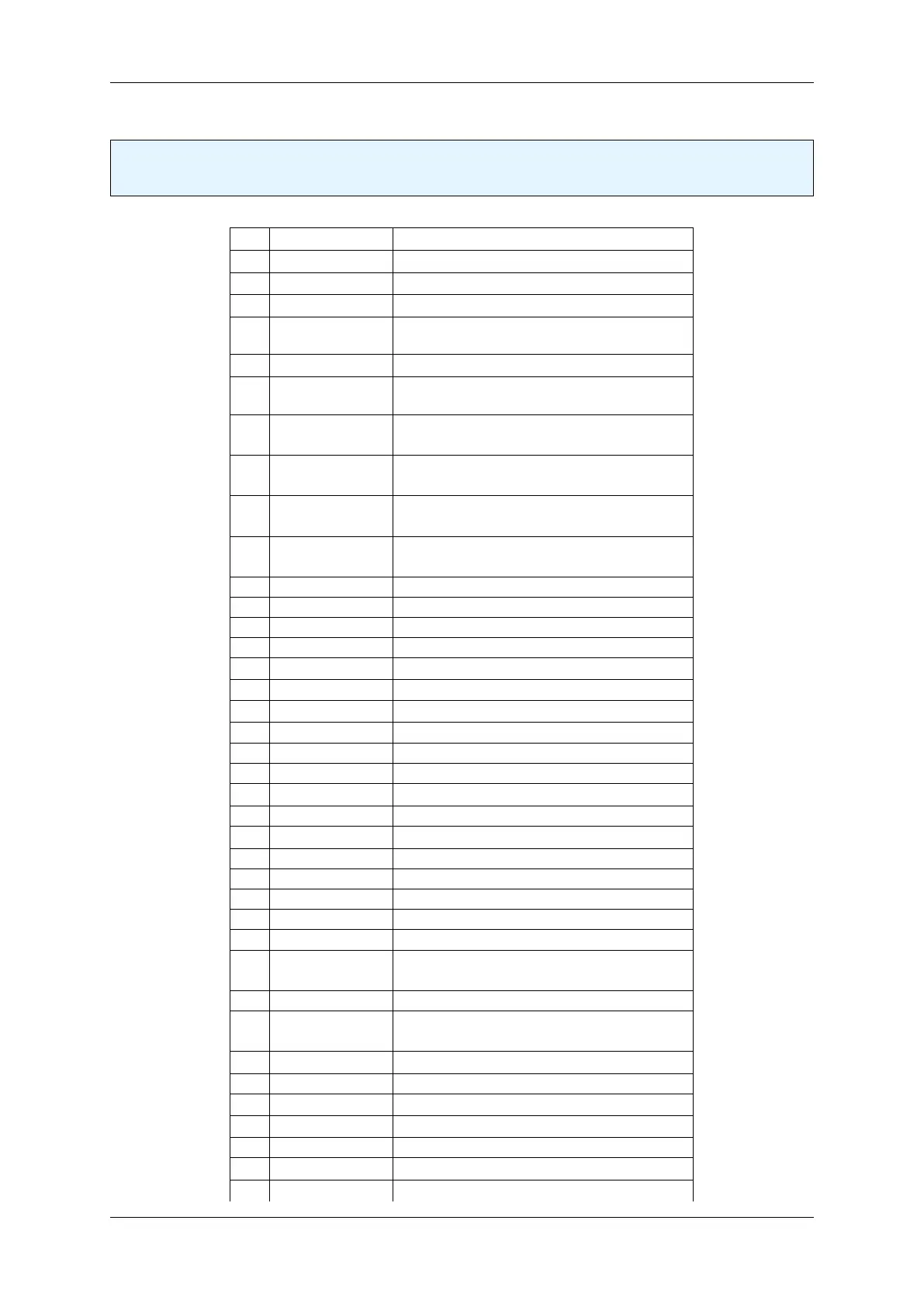

1.9.3.1 Pin assignment

Note

The red dot marks pin 1 of Hirose DF40GB(3.0)-70DS-0.4V.

Pin Signal Description

1 VCC_IN Input Voltage (5V-12V)

2 VCC3V3 Power Output, max. 10mA for customer use

3 VCC_IN Input Voltage (5V-12V)

4 I2C_SCL_USER I2C_USER (see details below)

LVCMOS 3.3V IO level

5 VCC_IN Input Voltage (5V-12V)

6 I2C_SDA_USER I2C_USER (see details below)

LVCMOS 3.3V IO level

7 DigIn0 Digital input (with level shifter)

Voltage reference VCC_IO

8 UART_RX LVCMOS 3.3V IO level

100 Ohm series resistor placed on mainboard

9 DigIn1 Digital input (with level shifter)

Voltage reference VCC_IO

10 UART_TX LVCMOS 3.3V IO level

100 Ohm series resistor placed on mainboard

11 GND Ground

12 GND Ground

13 GND Ground

14 GND Ground

15 PCIe_CLK_P PCIE_CLK + (differential)

16 - Do not connect, internal use

17 PCIe_CLK_N PCIE_CLK - (differential)

18 - Do not connect, internal use

19 GND Ground

20 GND Ground

21 PCIe_TX0_P PCIe Transmitter (differential)

22 - Do not connect, internal use

23 PCIe_TX0_N PCIe Transmitter (differential)

24 - Do not connect, internal use

25 GND Ground

26 GND Ground

27 GND Ground

28 GND Ground

29 DigIn2 Digital input (with level shifter)

Voltage reference VCC_IO

30 GND Ground

31 DigIn3 Digital input (with level shifter)

Voltage reference VCC_IO

32 PCIe_RX3_P PCIe Receiver (differential)

33 GND Ground

34 PCIe_RX3_N PCIe Receiver (differential)

35 PCIe_TX1_P PCIe Transmitter (differential)

36 GND Ground

37 PCIe_TX1_N PCIe Transmitter (differential)

38 PCIe_RX0_P PCIe Receiver (differential)

MATRIX VISION GmbH

Loading...

Loading...