Broadcom 96xx User Guide

Broadcom

®

96xx PCIe 4.0, 24G SAS MegaRAID

™

and eHBA Tri-Mode Storage Adapters

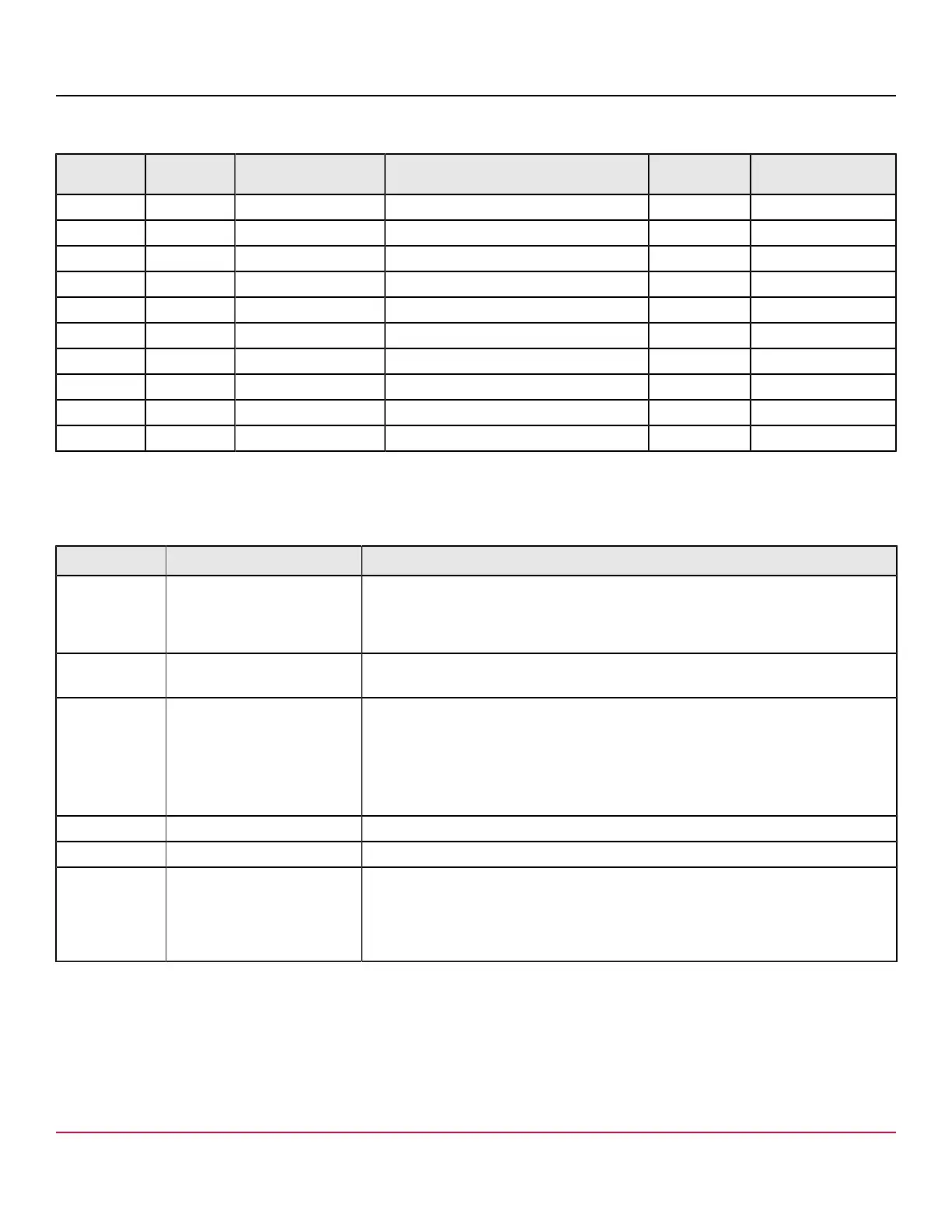

Table 12: Sideband Signal Pinout

Connector

A Side

Connector

B Side

Sideband or Vendor

Specific Pin Number

UBM Assignments Direction Resistor Value

A8 A26 7 BP_TYPE Input 100-kΩ pull-down

A9 A27 4 2W_RESET# Output 2.0-kΩ pull-up

A10 A28 3 GND — —

A11 A29 + REFCLK+ Output —

A12 A30 – REFCLK- Output —

B8 B26 0 2W_CLK Input/Output 2.0-kΩ pull-up

B9 B27 1 2W_DATA Input/Output 2.0-kΩ pull-up

B10 B28 2 GND — —

B11 B29 5 PERST# Input/Output 2.0-kΩ pull-up

B12 B30 6 C_TYPE, D_INPL#, CHANGE_DET# Input/Output 10-kΩ pull-up

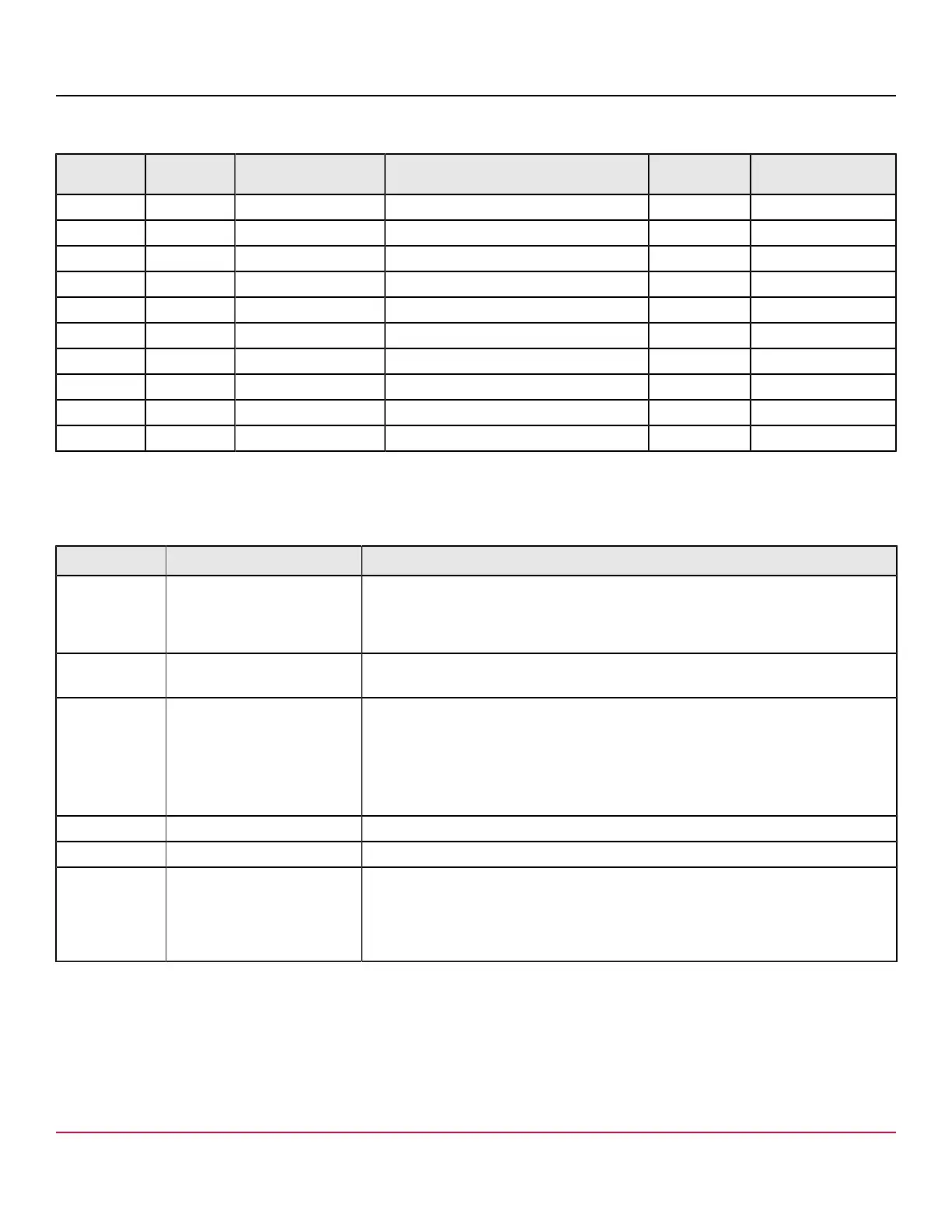

The following table describes the sideband signal pin settings.

Table 13: Sideband Management Pin Settings

Pin Name Settings Description

BP_TYPE

•

0: SGPIO

•

1: Two-wire interface

Indicates if the backplane uses SGPIO or two-wire interface for management.

To maintain backwards compatibility with SPGIO-based backplanes, the adapter has

a weak pull-down to default to SGPIO if the backplane does not explicitly drive the

signal.

2W_RESET#

•

0: Reset is asserted

•

1: Reset is not asserted

Optional reset driven by the host if the UBM target reports that the target can be

reset.

REFCLK+/- — PCIe REFCLK HCSL 100-MHz clock driven by the device side ports to PCIe devices

that require REFCLK.

If D_INPL# is 0 and BP_TYPE is 1, the adapter enables the REFCLK outputs for that

quad of high-speed lanes.

When BP_TYPE is 0 or the UBM Clock Routing bit on the backplane is 0, this output

is turned off.

2W_CLK —

The two-wire interface clock signal.

2W_DATA —

The two-wire interface data signal.

PERST#

•

0: Reset is asserted

•

1: Reset is not asserted

The adapter drives the PCIe RESET# signal.

This signal uses a clamp to ground so that the signal on the adapter powers up LOW

until backplane detection warrants the release of this signal for open-drain use. This

method ensures that PERST# does not deassert until the directly connected NVMe

drive is successfully detected.

Broadcom

96xx-MR-HBA-Tri-Mode-UG108

18

Loading...

Loading...