%

%

39

&" #"! !$! #

(98/12/10)

Address

Reset ConĆ

tent

Byte ForĆ

mat

3210

Read/

Write

Description

DestiĆ

nation

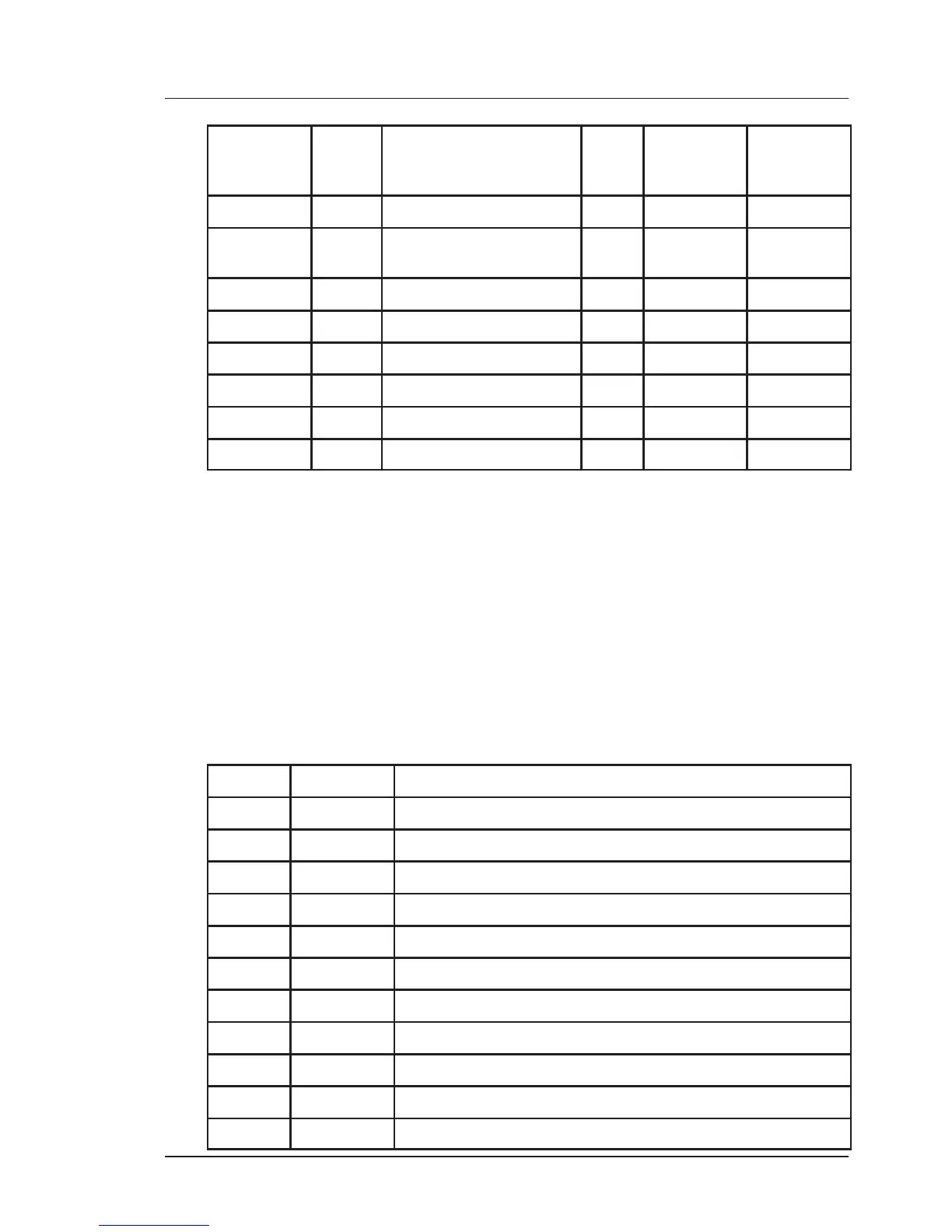

1F090040 CSR8 Missed frame counter R bbbb 00000000

1F090048 CSR9 Serial ROM and MII

manager R/W

R/W bbbb FFF097F0

1F090050 CSR10 Reserved bbbb undefined

1F090058 CSR11 General-purpose timer R/W bbbb FFFE0000

1F090060 CSR12 General-purpose port R/W bbbb FFFFFEXX

1F090068 CSR13 Reserved bbbb undefined

1F090070 CSR14 Reserved bbbb undefined

1F090078 CSR15 Watchdog timer R/W bbbb FFFFFEC8

DP83840 Physical Layer

The chip is a Physical Layer device for Ethernet 10BASE–T and

100BASE–X using category 5 Unshielded, Type 1 Shielded and

Fiber Optic cables

The chip interfaces the PMD sublayer through DP82223 Twisted

Pair Transceiver to the MAC layer 21140A through a Media

Independent Interface (MII)

The 32 word–wide MII status and control registers are accessible

through the serial management data interface pins MDC and MDIO

driven by 21140A via CSR9 register

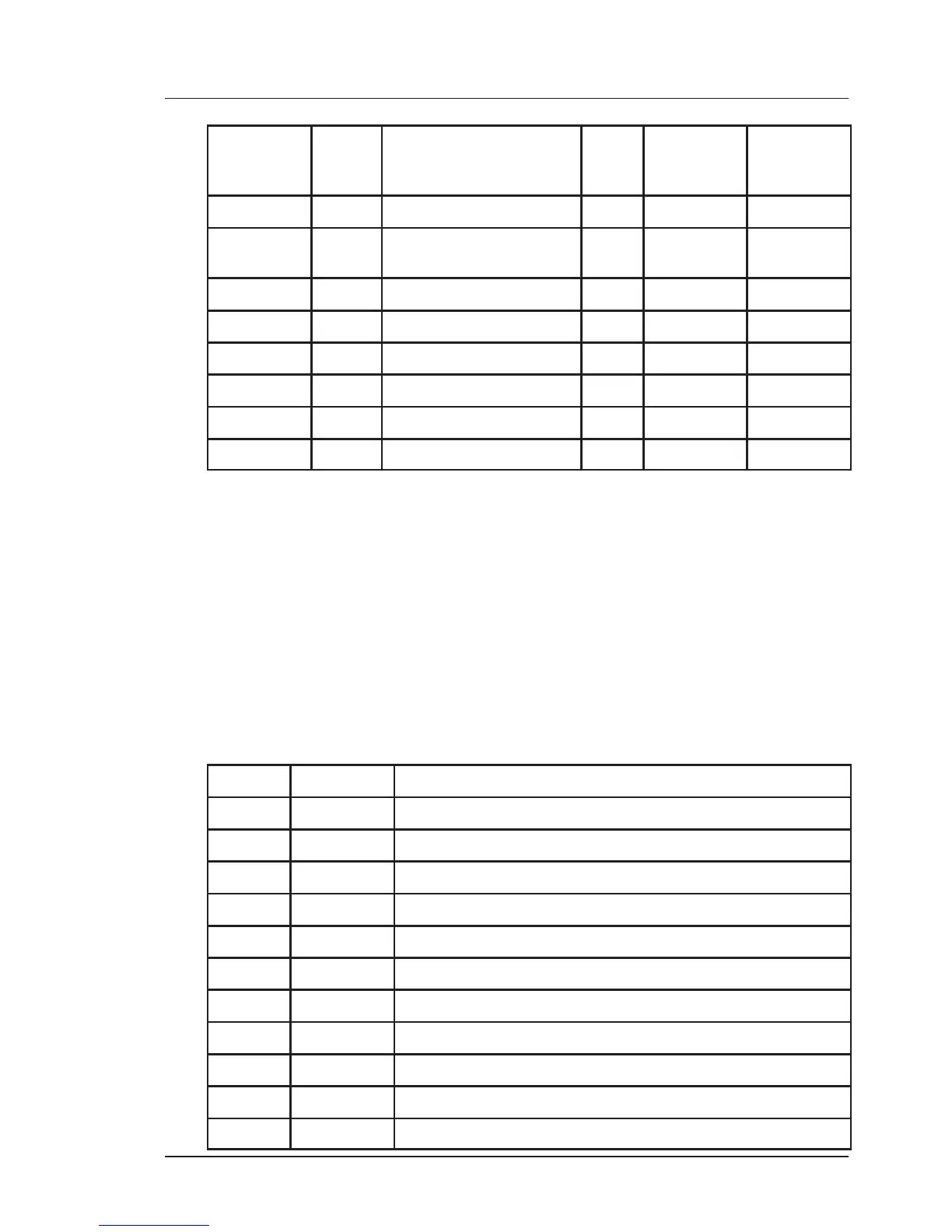

Physical Layer MII Register allocation

Address

Destination Description

00h BMCR Basic Mode Control Register

01h BMSR Basic Mode Status Register

02h PHYIDR1 PHY Identifier Register #1

03h PHYIDR2 PHY Identifier Register #2

04h ANAR Auto-Negotiation Advertisement Register

05h ANLPAR Auto-Negotiation Link Partner Ability Register

06h ANER Auto-Negotiation Expansion Register

07h–0fh -- Reserved

10h–11h -- Reserved

12h DCR Disconnect Counter Register

13h FCSR False Carrier Sense Counter Register

Loading...

Loading...