PRELIMINARY

Document type: Title: Revision date: Revision:

User's Manual (MUT) Mod. V1729 4 Channel 12 Bit Sampling ADC 22/06/2005 3

NPO: Filename: Number of pages: Page:

00109/04:V1729.MUTx/03 V1729_REV3.DOC 38 10

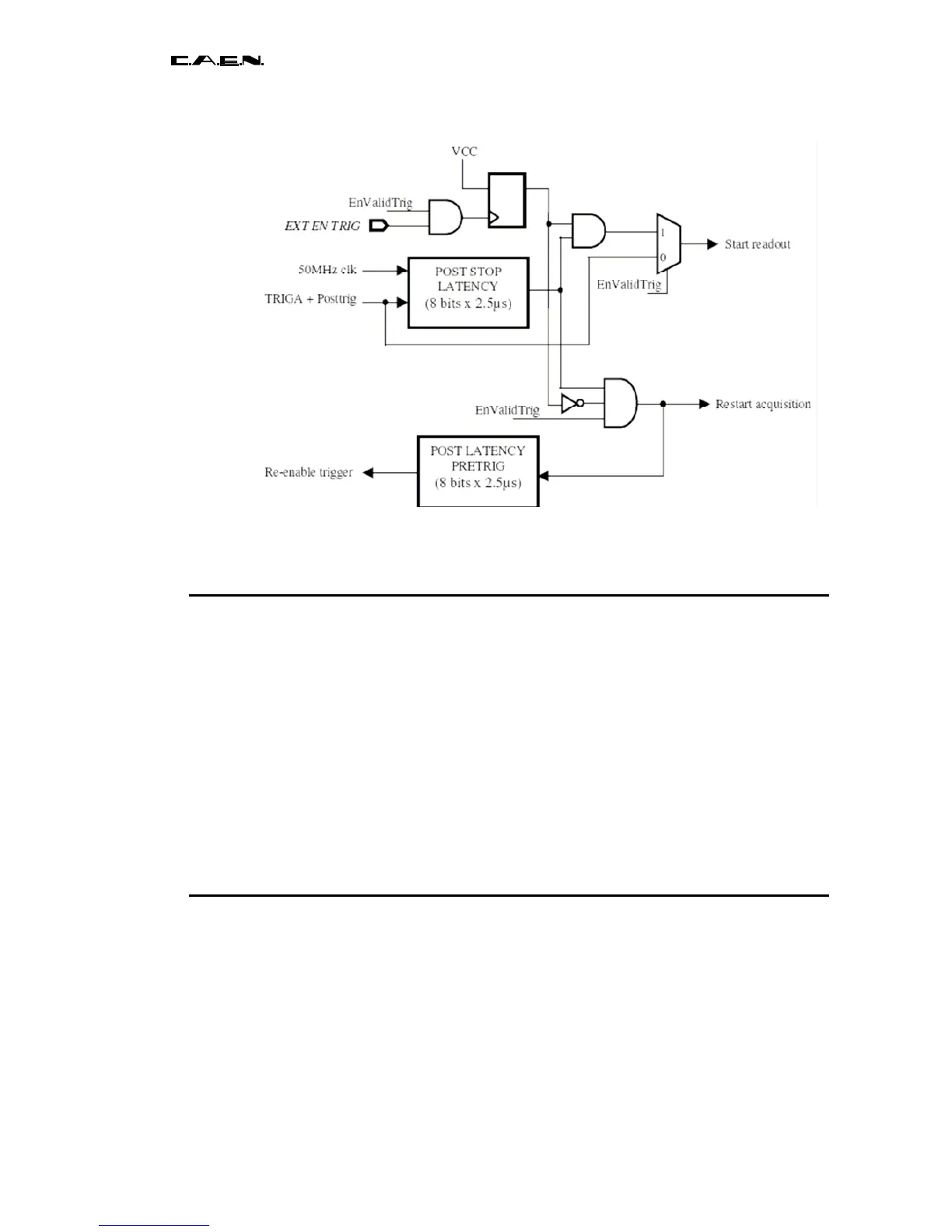

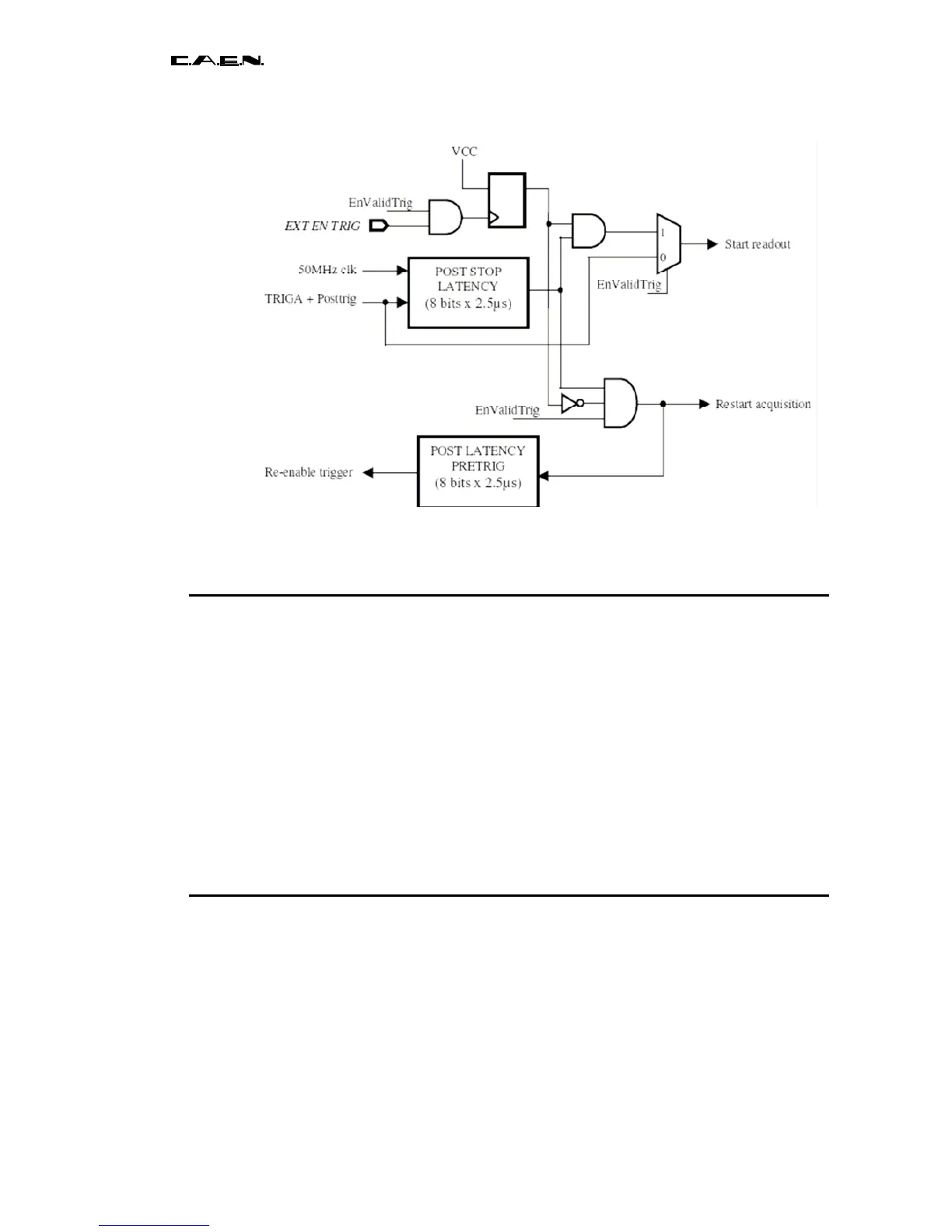

Fig. 2.4: simplified description of the trigger validation system.

2.3 Dead time at restarting of the acquisition; Pretrig

The frequency of the clock present on the board is relatively low (50MHz or 100MHz). In

order to be able to sample at a rate equal to or greater than the Giga-sample per second,

the MATACQ chips realize a virtual multiplication of frequency. This multiplication

requires a servo of which the control loop is interrupted at the time of the data read cycle.

At the time of the start of the acquisition, this servo has to get locked again. This

implicates a typical waiting of 150μs before being able to reach the optimum of the

sampling performances.

For this reason, at each restarting of the acquisition, the board must automatically

generate a dead time during which the triggers are not accepted.

This dead time is adjustable by the PRETRIG, from 1 to 65535 times the period of the

main clock. The minimal recommended PRETRIG values are therefore:

• 7500 (decimal) for a clock frequency of Fp = 50MHz.

• 15000 (decimal) for a clock frequency of Fp = 100MHz.

2.4 Standard acquisition sequence

Fig 2.4 shows the standard course of an acquisition :

The sequence begins with the initialization of the board by a RESET order.

Next, the different parameters which are not used with their default value must be

programmed (PRETRIG, POSTTRIG, TRIGGER TYPE, TRIGGER EDGE, MASK, NB

OF COL TO READ, FP FREQUENCY, …).

The starting order of the acquisition is next sent.

Loading...

Loading...