PRELIMINARY

Document type: Title: Revision date: Revision:

User's Manual (MUT) Mod. V1729 4 Channel 12 Bit Sampling ADC 22/06/2005 3

NPO: Filename: Number of pages: Page:

00109/04:V1729.MUTx/03 V1729_REV3.DOC 38 5

1. General description

1.1 Overview

The CAEN Mod. V1729 board is suited for acquisition of fast analog signals based on the

MATACQ (analog matrix) chip developed by collaboration of the CEA/DAPNIA and the

l’IN2P3/LAL [1].

The V1729 board, in the mechanical format VME double Europe, is compatible with

several standards of acquisition (VME A32/D32, A24/D16, and GPIB).

This board performs the coding of 4 analog channels of bandwidth up to 300MHz over 12

bits at a sampling frequency (Fe) reaching up to 2GHz and over a depth of 2520 usable

points.

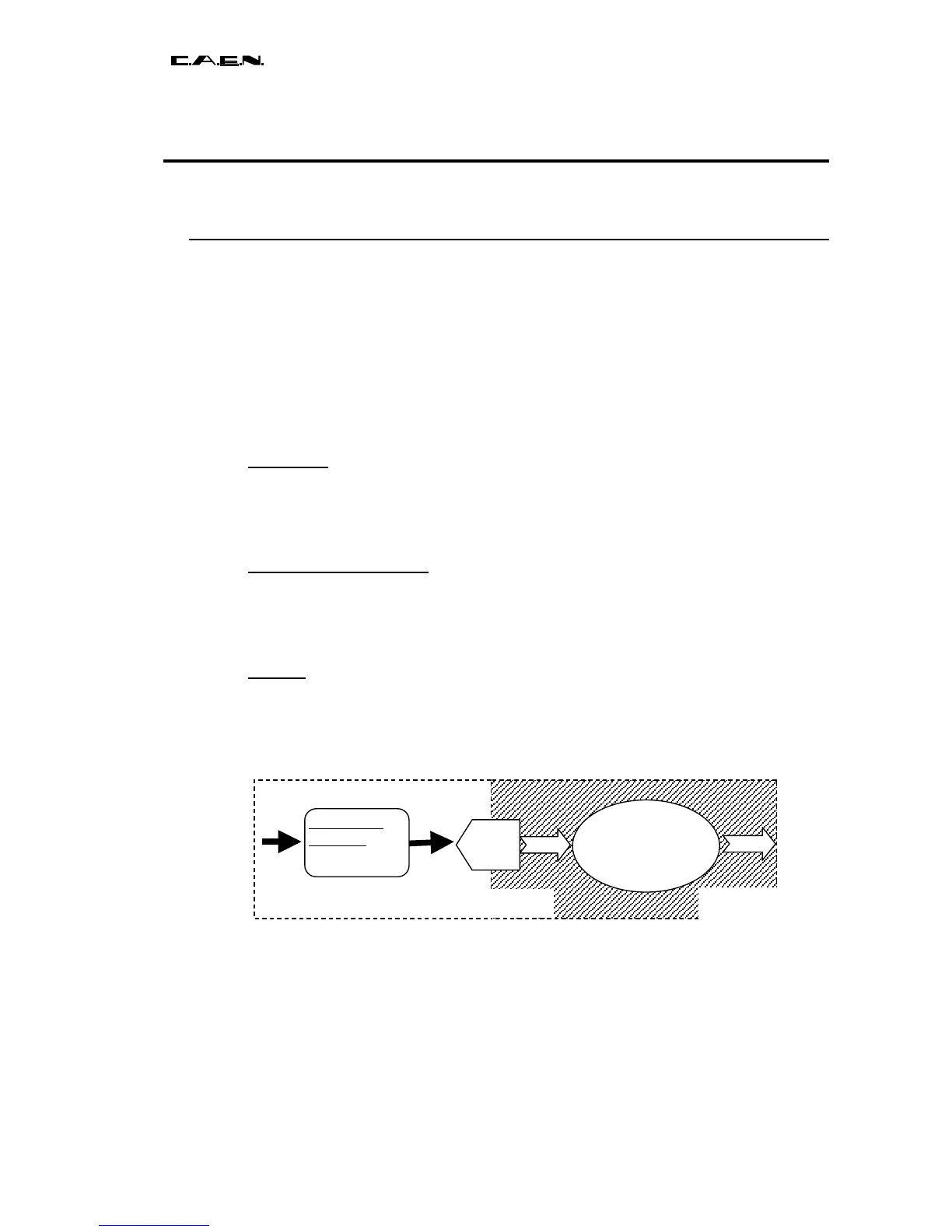

This operation is realized in three phases (see Fig 1.1):

Acquisition

:

the analog signal is continuously sampled at the frequency Fe in a circular analog

memory. The arrival of a trigger signal initiates the stopping phase of the sampling (2.1.1.

At the end of this phase, the state of the memory is set : it then contains the last 2560

points sampled (of which 2520 are valid).

Numerization and storage

:

after a stopping order of the acquisition, the samples stored under analog form in the

MATACQ chips are rapidly (650µs) re-read and coded into digital data over 12 bits, then

stored in a digital memory buffer. The acquisition is informed of the end of the coding

phase either by scrutation of an internal register, or by an interruption.

Reading

:

the memory buffer can then be re-read by the acquisition system. For an acquisition

system of VME A24-D16 standard, the latter operation lasts a few ms for the full readout

of a 4-channel board, which permits attaining an acquisition frequency of a few hundred

Hz for the acquisition of 2500 points per channel. With a high performance A32-D32

system, one should reach 1 kHz.

Fig. 1.1: data flow in the board

Loading...

Loading...