CY7C68013

Document #: 38-08012 Rev. *A Page 39 of 48

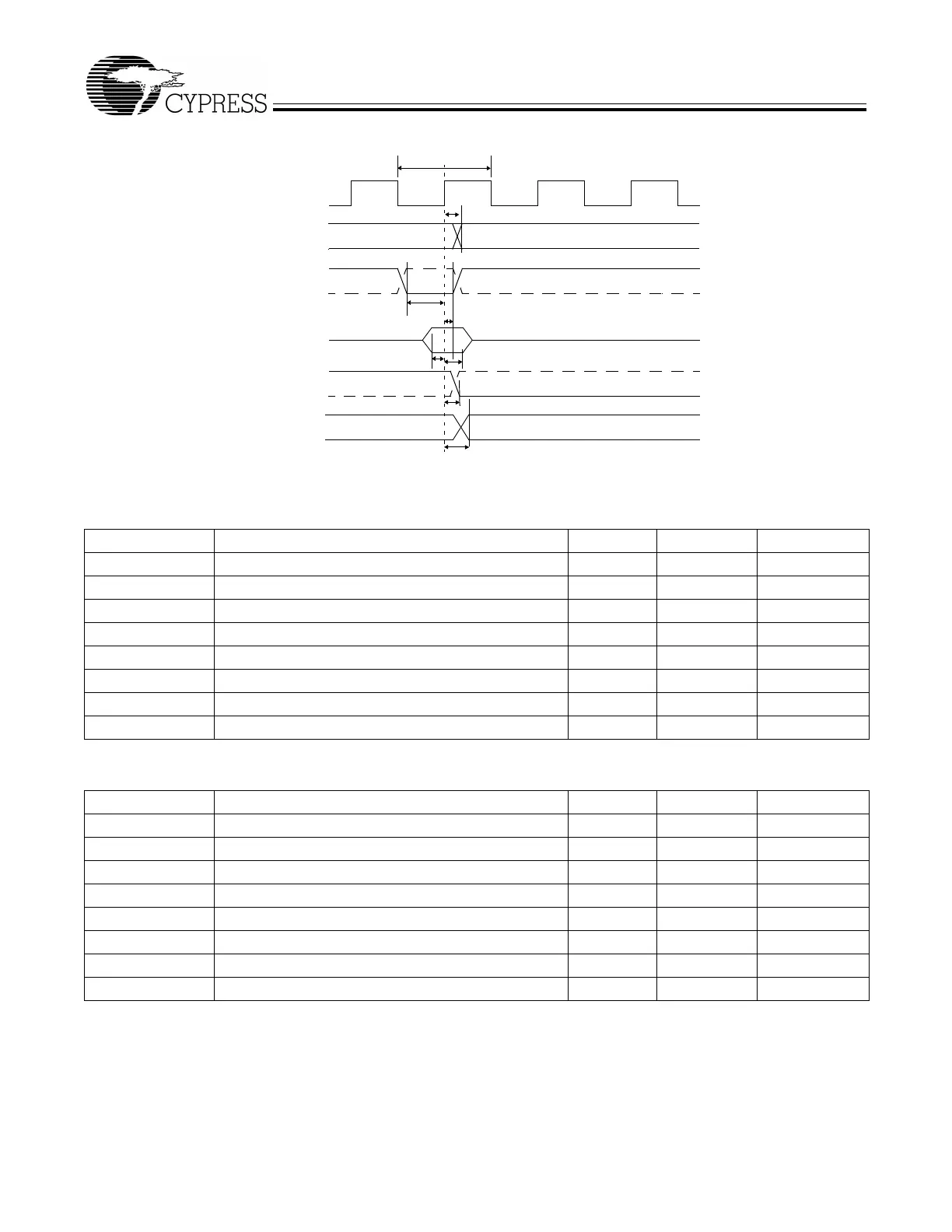

9.5 GPIF Synchronous Signals

Notes:

12. Dashed lines denote signals with programmable polarity

13. GPIF asynchronous RDY

x

signals have a minimum set-up time of 50 ns when using internal 48-MHz IFCLK.

14. IFCLK must not exceed 48 MHz.

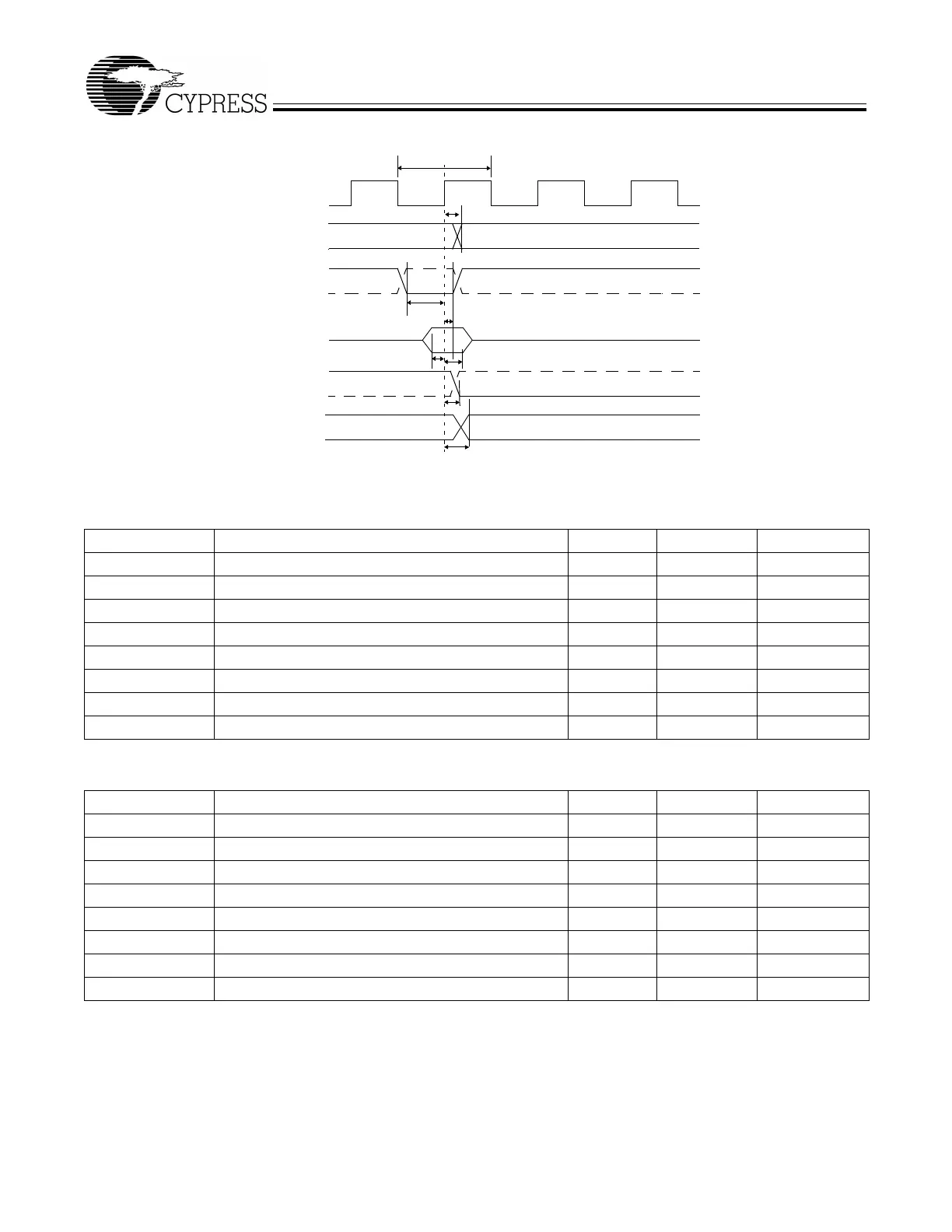

Table 9-4. GPIF Synchronous Signals Parameters with Internally Sourced IFCLK

[13, 14]

Parameter Description Min. Max. Unit

t

IFCLK

IFCLK Period 20.83 ns

t

SRY

RDY

X

to Clock Set-up Time 8.9 ns

t

RYH

Clock to RDY

X

0ns

t

SGD

GPIF Data to Clock Set-up Time 9.2 ns

t

DAH

GPIF Data Hold Time 0 ns

t

SGA

Clock to GPIF Address Propagation Delay 7.5 ns

t

XGD

Clock to GPIF Data Output Propagation Delay 11 ns

t

XCTL

Clock to CTL

X

Output Propagation Delay 6.7 ns

Table 9-5. GPIF Synchronous Signals Parameters with Externally Sourced IFCLK

[14]

Parameter Description Min. Max. Unit

t

IFCLK

IFCLK Period 20.83 200 ns

t

SRY

RDY

X

to Clock Set-up Time 2.9 ns

t

RYH

Clock to RDY

X

3.7 ns

t

SGD

GPIF Data to Clock Set-up Time 3.2 ns

t

DAH

GPIF Data Hold Time 4.5 ns

t

SGA

Clock to GPIF Address Propagation Delay 11.5 ns

t

XGD

Clock to GPIF Data Output Propagation Delay 15 ns

t

XCTL

Clock to CTL

X

Output Propagation Delay 10.7 ns

DATA(output)

t

XGD

IFCLK

RDY

X

DATA(input)

valid

t

SRY

t

RYH

t

IFCLK

t

SGD

CTL

X

t

XCTL

t

DAH

N

N+1

GPIFADR[8:0]

t

SGA

Figure 9-4. GPIF Synchronous Signals Timing Diagram

[12]

Loading...

Loading...