CY7C68013

Document #: 38-08012 Rev. *A Page 44 of 48

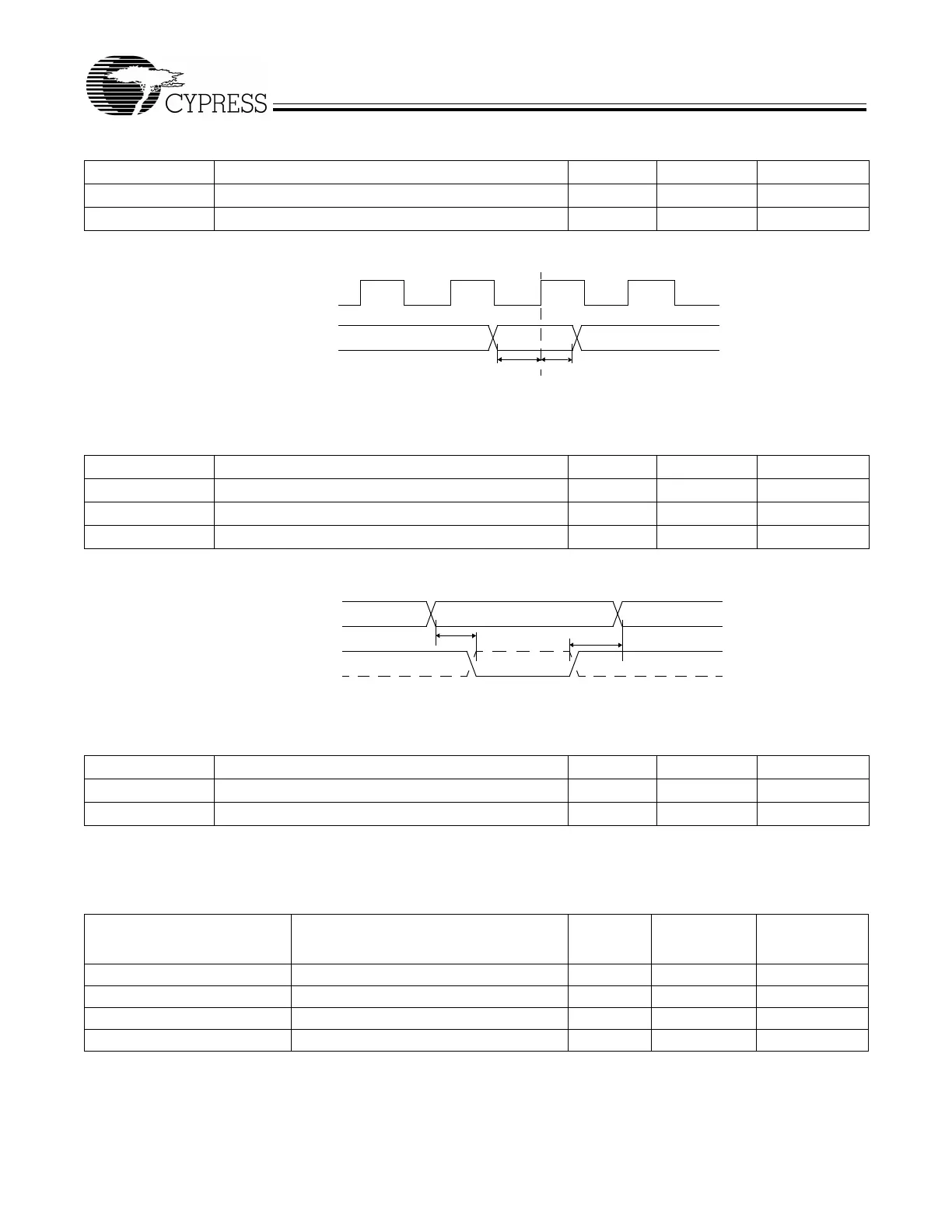

9.14 Slave FIFO Synchronous Address

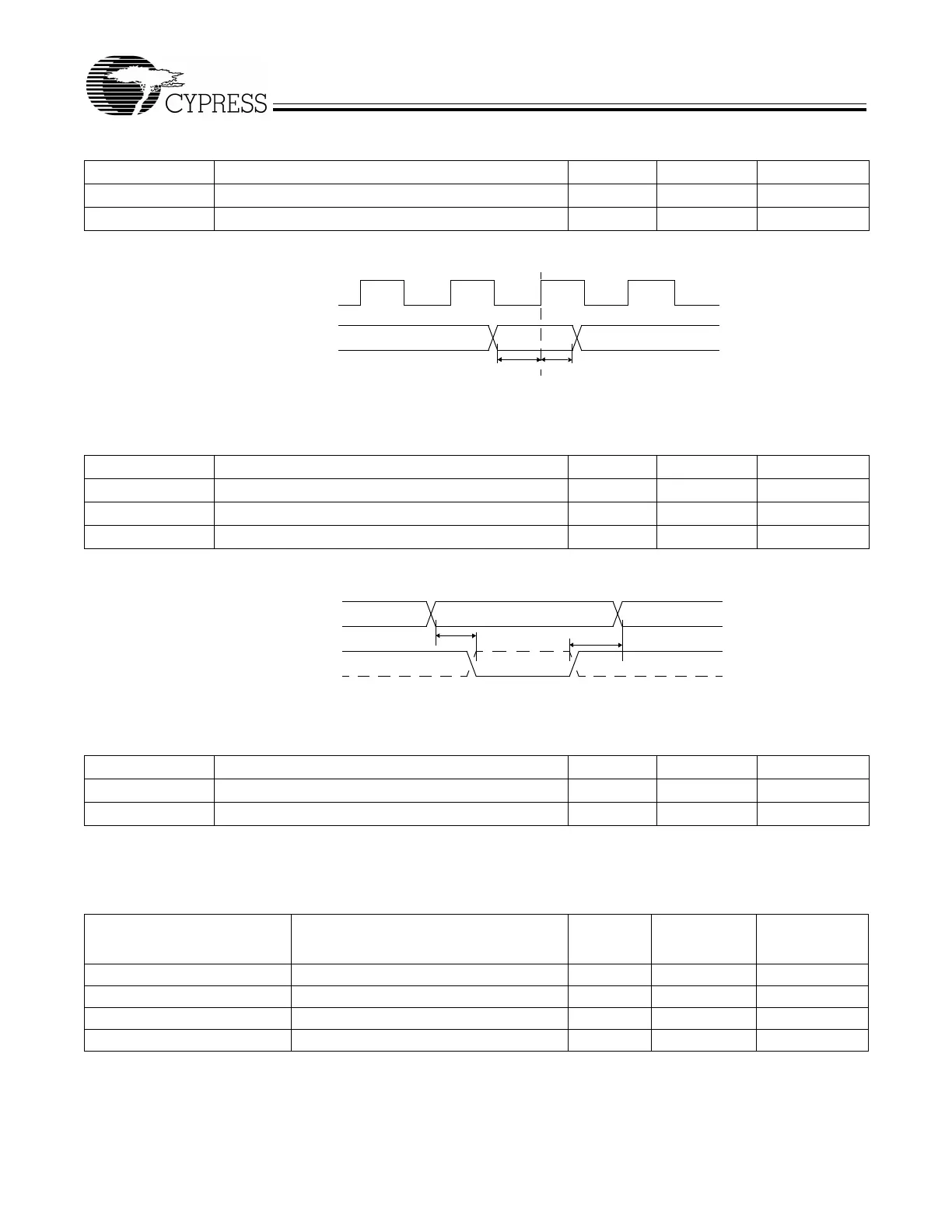

9.15 Slave FIFO Asynchronous Address

10.0 Ordering Information

Table 9-16. Slave FIFO Address to Flags/Data Parameters

Parameter Description Min. Max. Unit

t

XFLG

FIFOADR[1:0] to FLAGS Output Propagation Delay 10.7 ns

t

XFD

FIFOADR[1:0] to FIFODATA Output Propagation Delay 14.3 ns

Table 9-17. Slave FIFO Synchronous Address Parameters

[14]

Parameter Description Min. Max. Unit

t

IFCLK

Interface Clock Period 20.83 200 ns

t

SFA

FIFOADR[1:0] to Clock Set-up Time 25 ns

t

FAH

Clock to FIFOADR[1:0] Hold Time 10 ns

Table 9-18. Slave FIFO Asynchronous Address Parameters

[15]

Parameter Description Min. Max. Unit

t

SFA

FIFOADR[1:0] to RD/WR/PKTEND Set-up Time 10 ns

t

FAH

RD/WR/PKTEND to FIFOADR[1:0] Hold Time 10 ns

Table 10-1. Ordering Information

Ordering Code Package Type RAM Size # Prog I/Os

8051

Address

/Data Busses

CY7C68013-128AC 128 TQFP 8K 40 16/8 bit

CY7C68013-100AC 100 TQFP 8K 40 -

CY7C68013-56PVC 56 SSOP 8K 24 -

CY3681 EZ-USB FX2 Xcelerator Development Kit

IFCLK

SLCS/FIFOADR [1:0]

t

SFA

t

FAH

Figure 9-13. Slave FIFO Synchronous Address Timing Diagram

RD/WR/PKTEND

SLCS/FIFOADR [1:0]

t

SFA

t

FAH

Figure 9-14. Slave FIFO Asynchronous Address Timing Diagram

[12]

Loading...

Loading...