113

TCC8600 Pin Description

Doc. No AS-C-8600X-EA

TCC8600-00X-EAR

Rev. No 2.0

32-bit RISC Microprocessor for Host Player

Page 8 of 30

TELECHIPS Inc.

www.telechips.com

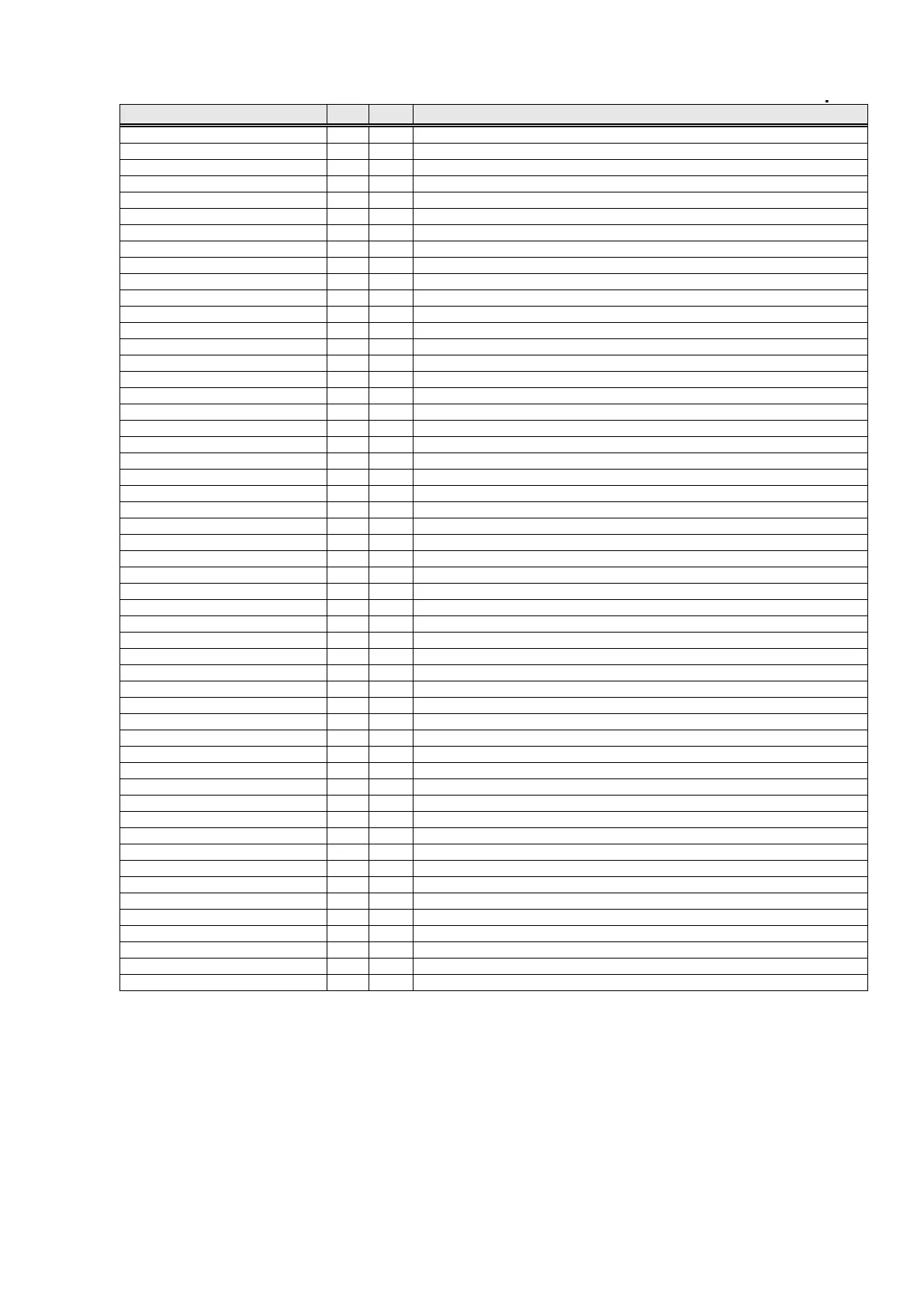

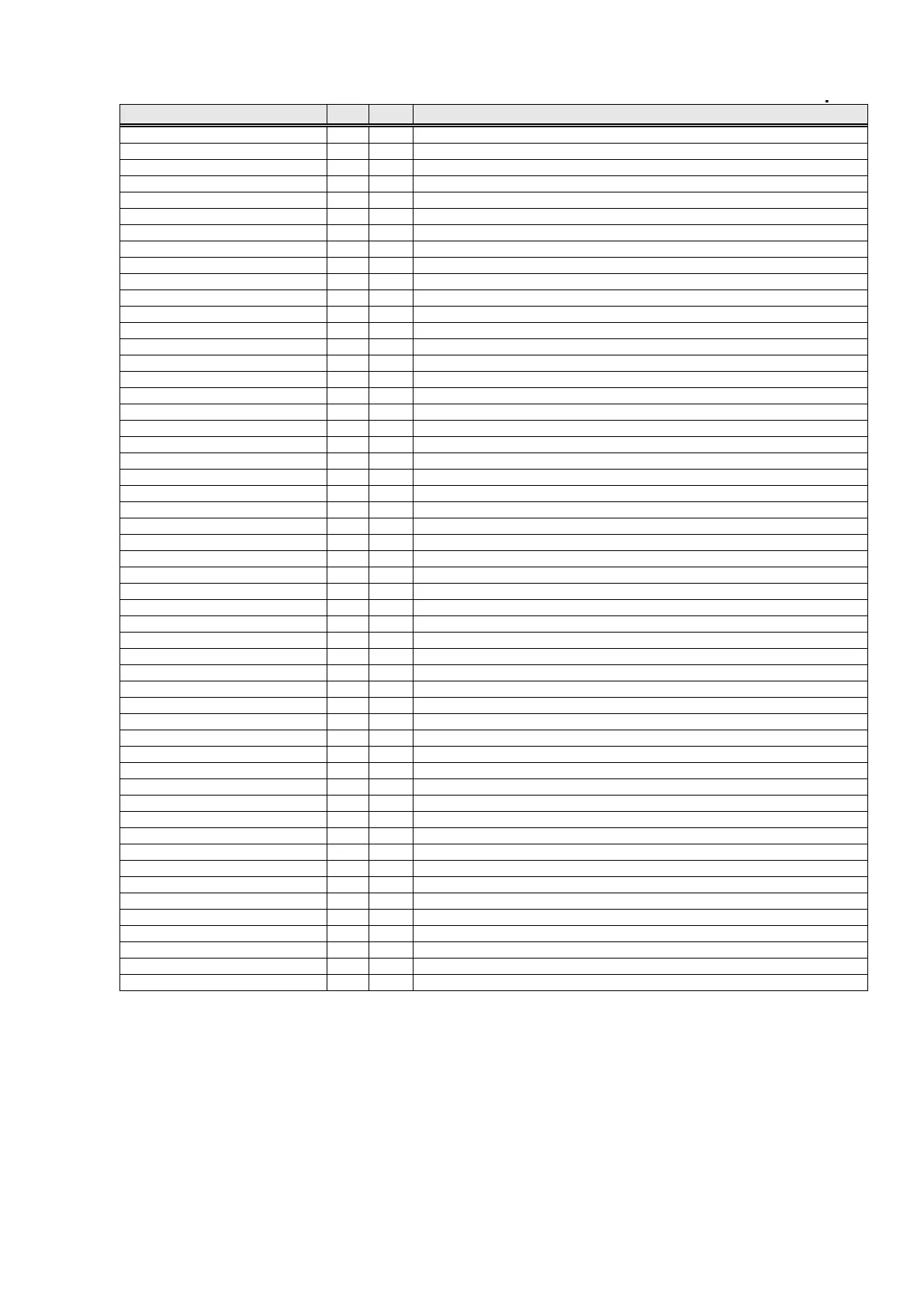

2.1 TCC8600 Pin Description

Table 2.1 TCC8600 Pin Description

Signal Name Pin# Type Description – TCC8600

SD_CLK 44 I/O SDRAM Clock

SD_CKE / GPIO_B[0] 46 I/O SDRAM Clock Enable signal. Active high. / GPIO_B[0]

SD_nCS / GPIO_B[1] 47 I/O Chip select signal for SDRAM, Active low / GPIO_B[1]

XA[21] / DQM[0] 42 I/O External Bus Address Bit [21] / Data I/O Mask 0

XA[20] / DQM[1] 41 I/O External Bus Address Bit [20] / Data I/O Mask 1

XA[19] / DQM[1] 39 I/O External Bus Address Bit [19] / Data I/O Mask 1

XA[18] / DQM[0] 38 I/O External Bus Address Bit [18] / Data I/O Mask 0

XA[17] / ND_CLE 37 I/O External Bus Address Bit [17] / CLE for NAND Flash

XA[16] / SD_nRAS / ND_ALE 36 I/O External Bus Address Bit [16] / SDRAM RAS signal / ALE for NAND Flash

XA[15] / SD_nCAS 35 I/O External Bus Address Bit [15] / SDRAM CAS signal

XA[14] / SD_BA[1] 34 I/O External Bus Address Bit [14] / SDRAM Bank Address 1

XA[13] / SD_BA[0] 33 I/O External Bus Address Bit [13] / SDRAM Bank Address 0.

XA[12] 32 I/O External Bus Address Bit [12]

XA[11] 31 I/O External Bus Address Bit [11]

XA[10] 30 I/O External Bus Address Bit [10]

XA[9] 29 I/O External Bus Address Bit [9]

XA[8] 28 I/O External Bus Address Bit [8]

XA[7] 27 I/O External Bus Address Bit [7]

XA[6] 23 I/O External Bus Address Bit [6]

XA[5] 22 I/O External Bus Address Bit [5]

XA[4] 21 I/O External Bus Address Bit [4]

XA[3] 20 I/O External Bus Address Bit [3]

XA[2] 19 I/O External Bus Address Bit [2]

XA[1] 18 I/O External Bus Address Bit [1]

XA[0] 17 I/O External Bus Address Bit [0]

XD[15] 16 I/O External Bus Data Bit [15]. Internal pull-up resistor enabled at reset.

XD[14] 15 I/O External Bus Data Bit [14]. Internal pull-up resistor enabled at reset.

XD[13] 14 I/O External Bus Data Bit [13]. Internal pull-up resistor enabled at reset.

XD[12] 13 I/O External Bus Data Bit [12]. Internal pull-up resistor enabled at reset.

XD[11] 12 I/O External Bus Data Bit [11]. Internal pull-up resistor enabled at reset.

XD[10] 11 I/O External Bus Data Bit [10]. Internal pull-up resistor enabled at reset.

XD[9] 10 I/O External Bus Data Bit [9]. Internal pull-up resistor enabled at reset.

XD[8] 6 I/O External Bus Data Bit [8]. Internal pull-up resistor enabled at reset.

XD[7] 5 I/O External Bus Data Bit [7]. Internal pull-up resistor enabled at reset.

XD[6] 4 I/O External Bus Data Bit [6]. Internal pull-up resistor enabled at reset.

XD[5] 3 I/O External Bus Data Bit [5]. Internal pull-up resistor enabled at reset.

XD[4] 2 I/O External Bus Data Bit [4]. Internal pull-up resistor enabled at reset.

XD[3] 128 I/O External Bus Data Bit [3]. Internal pull-up resistor enabled at reset.

XD[2] 127 I/O External Bus Data Bit [2]. Internal pull-up resistor enabled at reset.

XD[1] 126 I/O External Bus Data Bit [1]. Internal pull-up resistor enabled at reset.

XD[0] 125 I/O External Bus Data Bit [0]. Internal pull-up resistor enabled at reset.

nWE 48 I/O Static Memory Write Enable signal. Active low.

nOE 49 I/O Static Memory Output Enable signal. Active low.

ND_nWE / GPIO_B[7] 61 I/O NAND flash WE. Active low. / GPIO_B[7]

nCS[3] / ND_nOE[3] / GPIO_B[5] 53 I/O External Bus Chip Select [3] / NAND Flash Output Enable [3] / GPIO_B[5]

nCS[2] / ND_nOE[2] / GPIO_B[4] 52 I/O External Bus Chip Select [2] / NAND Flash Output Enable [2] / GPIO_B[4]

nCS[1] / ND_nOE[1] / GPIO_B[3] 51 I/O External Bus Chip Select [1] / NAND Flash Output Enable [1] / GPIO_B[3]

nCS[0] / ND_nOE[0] / GPIO_B[2] 50 I/O External Bus Chip Select [0] / NAND Flash Output Enable [0] / GPIO_B[2]

READY / MODE0 64 I Ready information from external device.

USBH1_DP / GPIO_B[26] 83 I/O USB Host Port 1 D+ signal / GPIO_B[26]

USBH1_DN / GPIO_B[27] 82 I/O USB Host Port 1 D- signal / GPIO_B[27]

USBH0_DP / GPIO_B[28] 80 I/O USB Host Port 0 D+ signal / GPIO_B[28]

USBH0_DN / GPIO_B[29] 79 I/O USB Host Port 0 D- signal / GPIO_B[29]

Loading...

Loading...