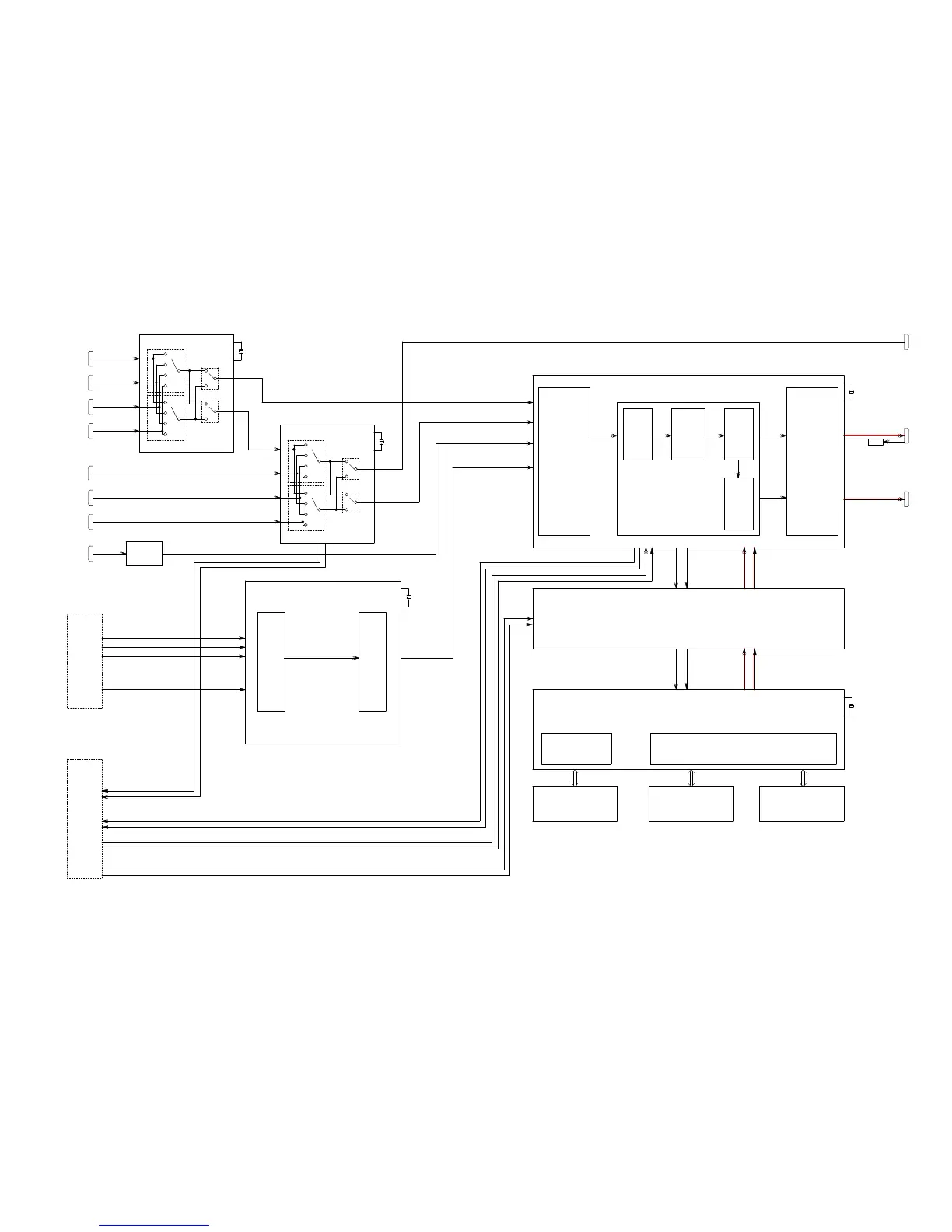

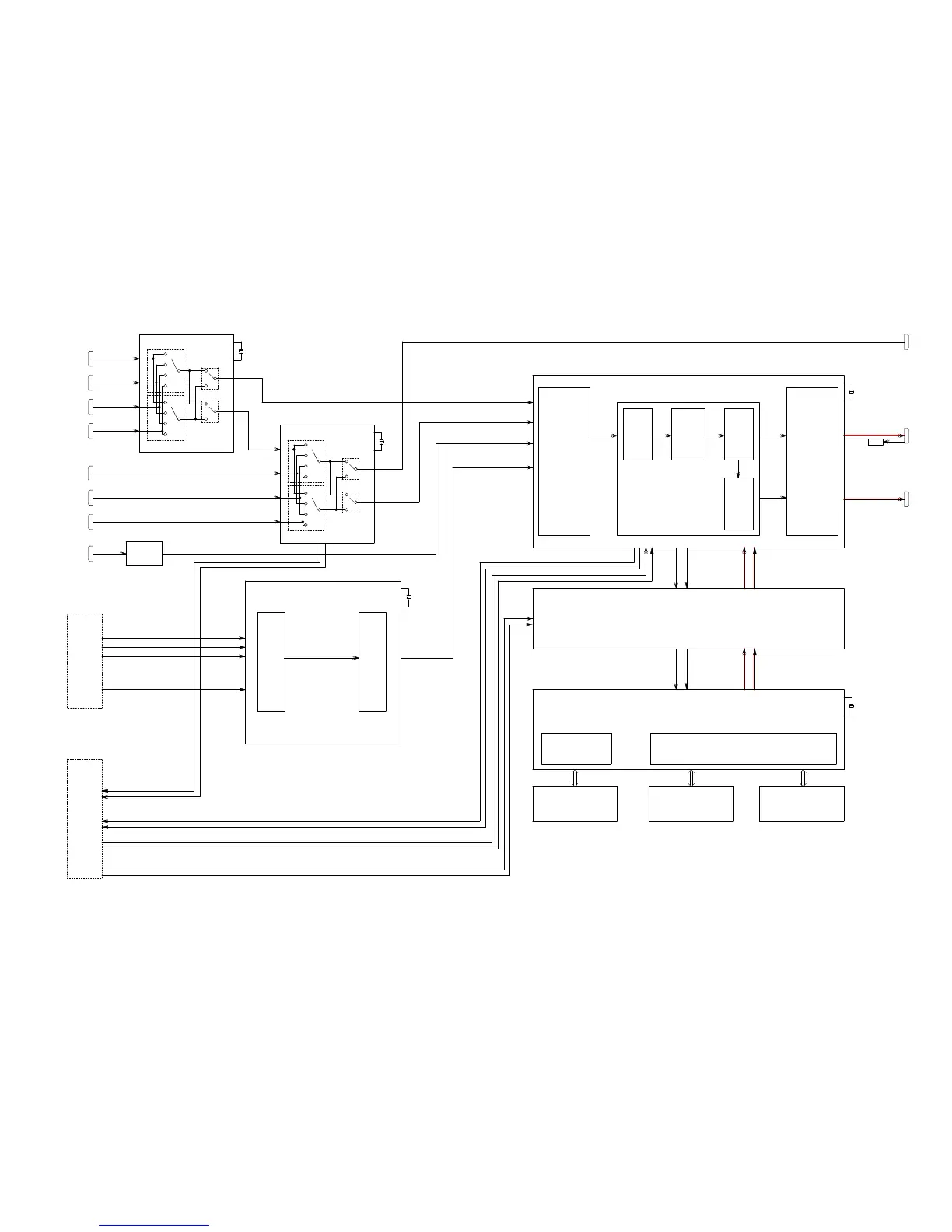

fig.22

MAIN

SUB

SUB

MAIN

HDMI OUT2

HDMI ZONE2

P0 TX

HDMI IN1

HDMI IN2

HDMI IN3

HDMI IN4

HDMI IN5

HDMI IN6

(CBL/SAT)

(DVD)

(BLU-RAY)

(GAME)

(MEDIA Player)

(AUX2)

HDMI IN7

(CD)

HDMI IN8

(AUX1)

AD8195

Buffer

HDMI OUT1

ARC

HDMI SW2(MN864777)

HDMI TX(MN864777)

DEC_Y_IN

DEC_PB_IN

DEC_PR_IN

DEC_CVBS_IN

VIDEO BLOCK

VIDEO PLD

AD55/058Z-0(ADV8003-8B)

DDR2 SDRAM

512M

DDR2 SDRAM

512M

S. FLASH

128M

MX25L12845EMI-10G

A3R12E40CBF-8E A3R12E40CBF-8E

P3 RX

P2 RX

P1 RX

P0 RX

P0 TX

P1 TX

P3 RX

P2 RX

P1 RX

P0 RX

P0 TX

P

1 TX

P1 RX

P0 RX

P3 RX

P2 RX

ADV7850

VIDEO SIGNAL OUT

VIDEO INPUT

DIGITAL AUDIO BLOCK

ANALOG

HDMI Rx

P1 TX

Matrix SW

600MHz

Rxlink0 Txlink0

Txlink1

4K/2K

Up Scaler

HDMI Tx

Matrix SW

600MHz

600MHz

DDR2 INTERFACE

CONTROL

Video Processor(1080P, OSD, IP Conv,)

4K/2K

4K/2K

WITH TMDS

EPM570F256C4N

Z2HDMISPDIF

RXI2S0~3, RXSPDIF

HDMI SW1(MN864777)

920PCK

920VD0~7

920PCK

920VD0~7

TXDATA0

TXBCK, TXLRCK

TXDATA0

TXBCK, TXLRCK

RXMCK, RXBCK, RXLRCK, RXINT0

RXMCK, RXBCK, RXLRCK, RXINT0

B0~B7/G0~G7/R0~R7

PCK/HSYNC/VSYNC/DE

B0~B7/G0~G7/R0~R7

PCK/HSYNC/VSYNC/DE

B0~B7/G0~G7/R0~R7

PCK/HSYNC/VSYNC/DE

B0~B7/G0~G7/R0~R7

PCK/HSYNC/VSYNC/DE

RXI2S0~3, RXSPDIF

Z2_HAINT

105

119

27.000MHz

27.000MHz

27.000MHz

27.000MHz

27.000MHz

AVR-X4100W HDMI VIDEO BLOCK

69

Loading...

Loading...