Appendix

Appendix

User's Manual

BAB 740

7—5

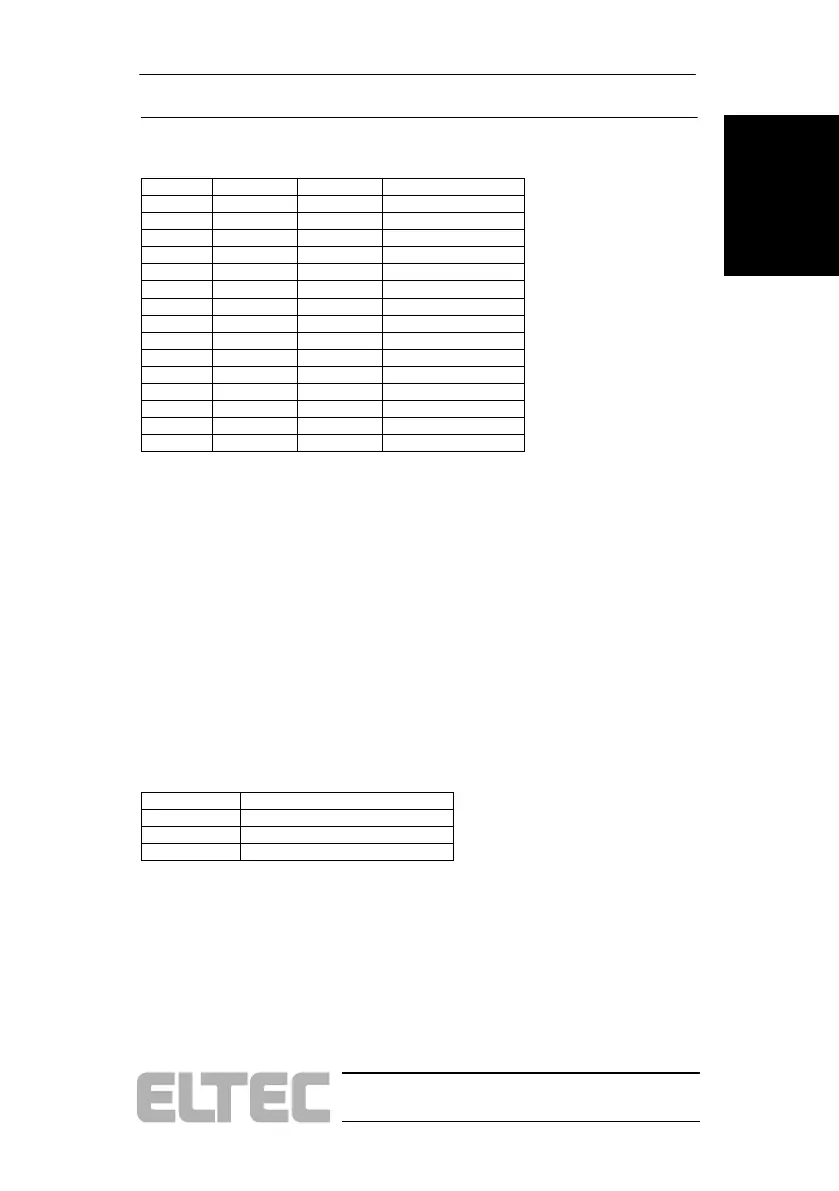

Table 32: Interrupt

Priority ISA IRQ PCI IRQ Source

1

INT 0 Timer 0 (Ticker)

2

INT 1 Keyboard

3

INT 8

4

INT 9 ESCC

5

INT10 INT A PMC #1

6

INT 11 INT B SCSI or PMC #2

7

INT 12

8

INT 13

9

INT 14 INT C Ethernet

10

INT 15 INT D VME

11

INT 3 Serial #2

12

INT 4 Serial #1

13

INT 5 RTC

14

INT 6 Floppy

15

INT 7 Parallel Port

7.1.4 SRAM/RTC

A indirect addressing scheme is used to access the M48T59Y

SRAM/RTC. To access the SRAM/RTC the desired address first

must be written to I/O address $70 and $71. Then the data can be

accessed via I/O address $76. The interrupt output of the M48T59Y

is connected with the INT5 input of the interrupt controller. It may

be used to generate periodic interrupts or watchdog interrupts.

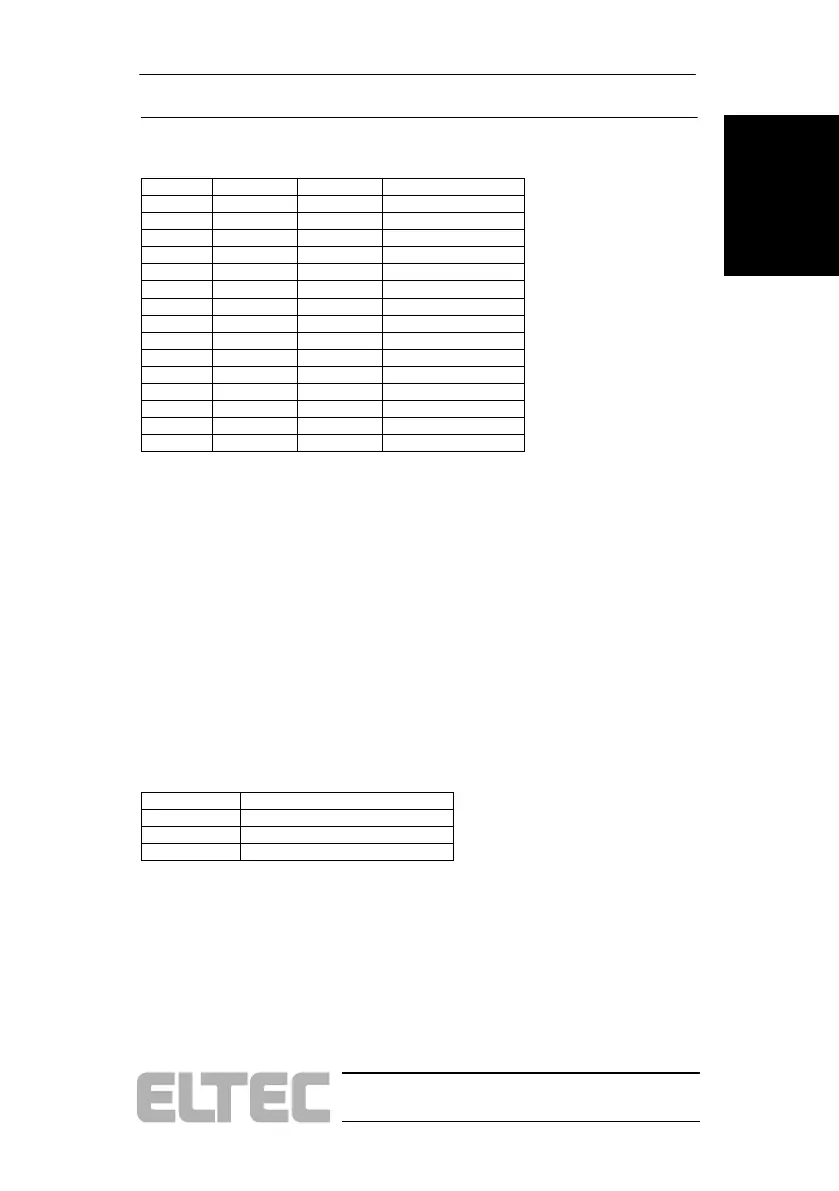

Table 33: SRAM/RTC Address Assignment

I/O Address Description

$070 SRAM/RTC LSB Address

$071 SRAM/RTC MSB Address

$076 SRAM/RTC Data

Loading...

Loading...