Appendix

Appendix

User's Manual

BAB 740

7—6

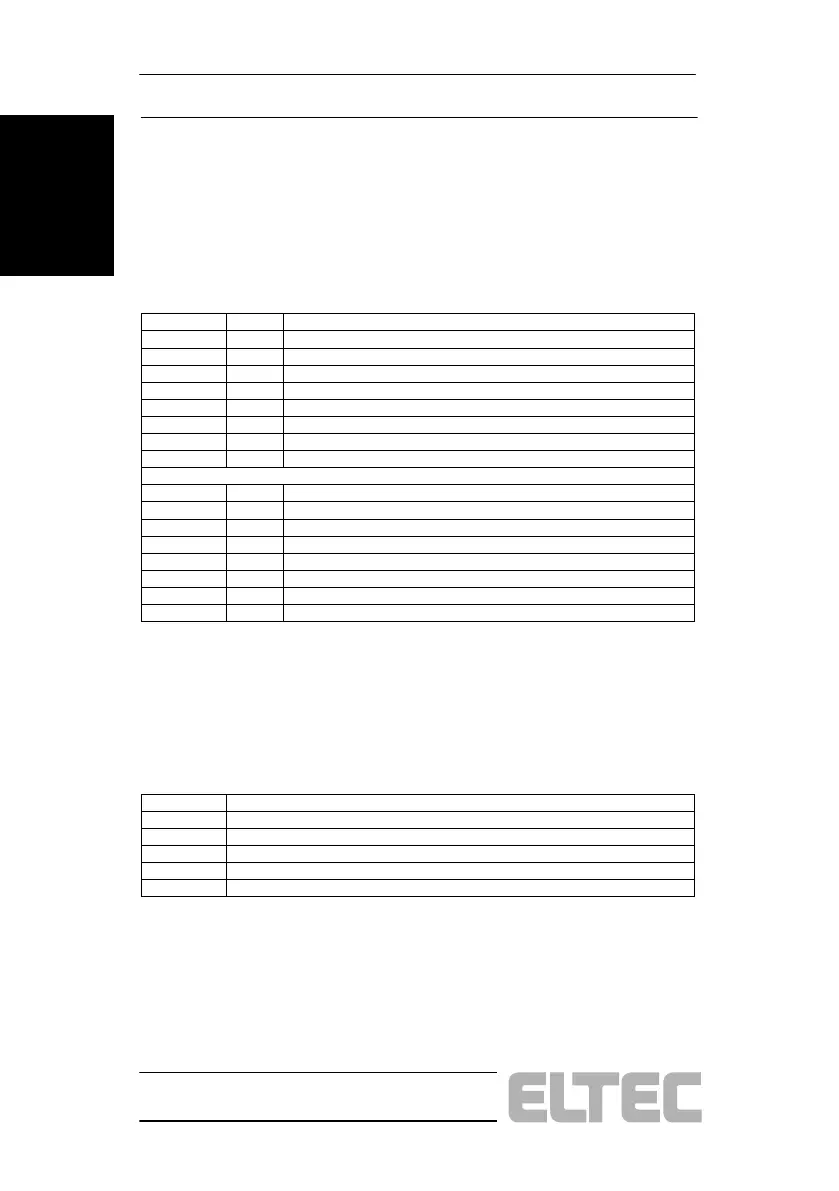

7.1.5 GPIO Use

The GPIOs of the Super-I/O are used for the following purposes:

Table 34: GPIO Usage

Name Type Function

GPIO10 - not used

GPIO11 I CPU Bus Speed (0 = 83 MHz; 1 = 66MHz)

GPIO12 I L2 Cache Size (0 = 256 KByte; 1 = 512KByte)

GPIO13 I/O I2C Data for SPD of 2nd SODIMM

GPIO14 O I2C Clock for SPD of 2nd SODIMM

GPIO15 I/O I2C Data for SPD of 1st SODIMM, ELTEC Revision EEPROM

GPIO16 O I2C Clock for SPD of 1st SODIMM, ELTEC Revision EEPROM

GPIO17 - not used

GPIO20 - not used

GPIO21 - not used

GPIO22 - not used

GPIO23 - not used

GPIO24 I HEX Switch LSB

GPIO25 I HEX Switch

GPIO26 I HEX Switch

GPIO27 I HEX Switch MSB

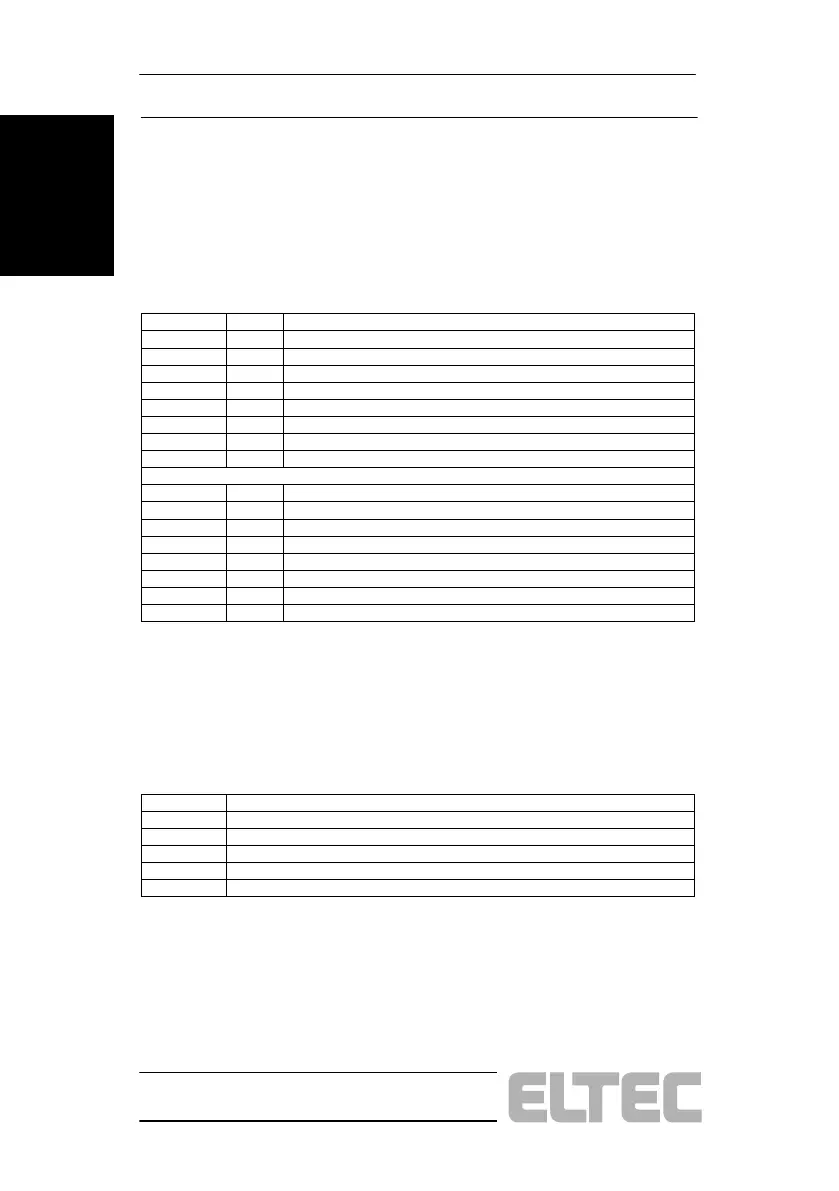

7.1.6 Super-I/O Power-on Strappings

The Super-I/O wakes up in the following configuration:

Table 35: Super-I/O Wake Up Configuration:

Pin Configuration

CFG0 FDC, KBC and RTC inactive

CFG1 No X-Bus Data Buffer

CFG3,2 Clock source is 24 MHz fed via X1 Pin

BADDR1,0 PnP Motherboard, Wake in Config state, Index 015Ch

SELCS /CS0 on /CS0 pin

Loading...

Loading...