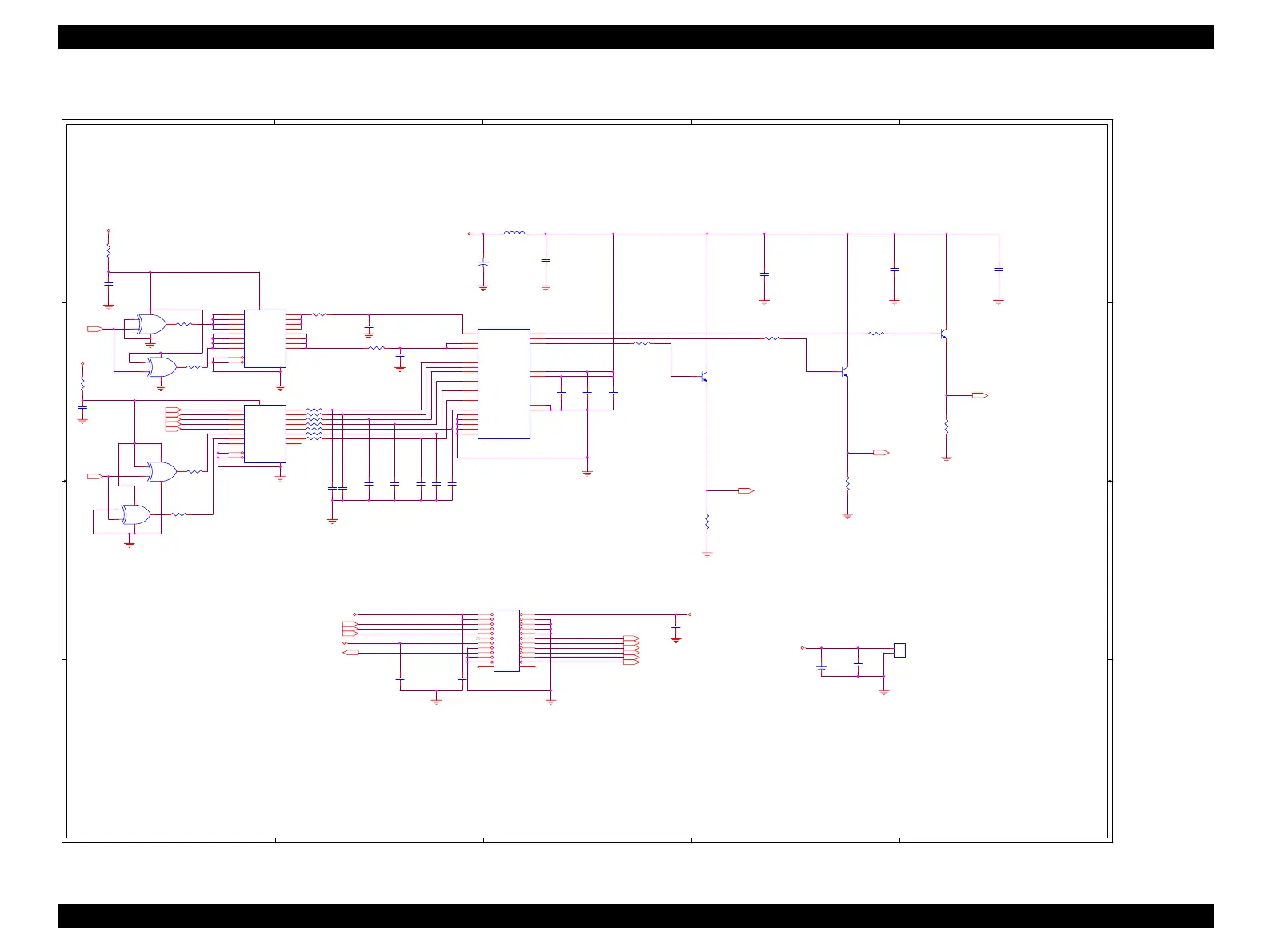

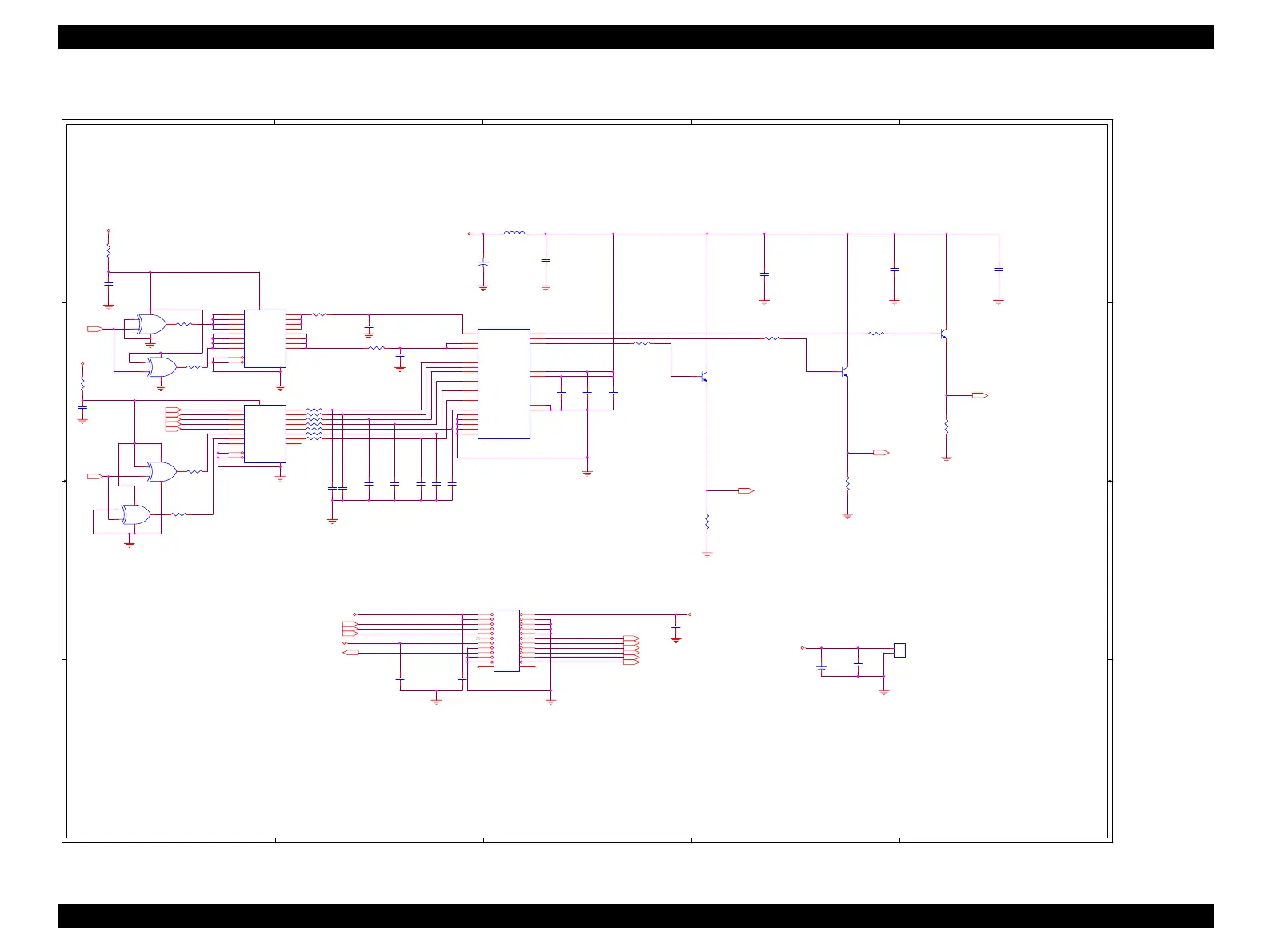

EPSON Perfection 1670 Photo/Perfection 1270 Revision B

APPENDIX Circuit Diagrams 44

CCD

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

OSR

OSG

OSB

20020910

*Del U11C

*Change Net Name PHISHR-->PHITGR

*Reserve U11C,U12E,U12F input pin

20020911

*Add PHI2 signal with U11.3 and U11.13

*Remove the J1 PIN assignment

*Del C4

*Remove the U11,U12 logic gate

VCC5VR

L15V

A12V

VCC5VR

VCC5VR

A12V

L15V

R7 51

C43

0.1U Z

Q3

2N3904

1

32

+

C15

47U

25V

12

U14A

7486

1

2

4

53

C41

0.1U Z

C51

20P J

C50

680P J

R15 100

C48

47P J

C34

0.1U Z

U22

SN74AHCT244

2

4

6

8

11

13

15

17

1

19

18

16

14

12

9

7

5

3

20

10

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

OE1

OE2

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

GND

Q2

2N3904

1

32

C33

0.1U Z

R16 100

C32

0.1U Z

R23 100

C36

0.1U Z

Q1

2N3904

1

32

C52

100PJ

C47

47P J

C44

0.1U Z

J1

20K0276022

1

3

5

7

9

11

13

15

17

19

21

2

4

6

8

10

12

14

16

18

20

22

G1 G2

1

3

5

7

9

11

13

15

17

19

21

2

4

6

8

10

12

14

16

18

20

22

G1 G2

R24 100

C35

0.1U Z

R20 100/0603

C53

100P J

C46

47P J

R13

2K/0603

R6 0

U12A

7486

1

2

4

53

R1 100

C55

0.1U Z

R21 100/0603

C54

100P J

R17

2K/0603

R5 0

R9 33

R22 100

B1 120 OHM/0805

C38

0.1U Z

U21

SN74ACT244

2

4

6

8

11

13

15

17

1

19

18

16

14

12

9

7

5

3

20

10

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

OE1

OE2

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

GND

R10 20

U11A

7486

1

2

4

53

+

C1

47U

25V

12

C42

0.1U Z

R18

2K/0603

R14 33

C45

0.1U Z

U4

CCD8861_0

21

12

8

22

1

13

14

6

3

11

15

18

20

10

7

9

16

17

2

4

19

5

PH3

NC

PH1

NC

NC

TGG

TGB

VoutB

PH1L

NC

Vdc

GND

PH4

TGR

GND

PH2

NC

VoutG

PH2L

Vdc

PHRS

VoutR

R19 100/0603

R8

0/0603

R11

0/0603

U13A

7486

1

2

4

53

C40

0.1U Z

C49

680P J

J2

1R2P/RT/D2

1

2

R12 100

PHI1

PHIRS

PHIRS

PHICP

PHITGR

PHI1L

OSB

OSG

OSR

PHITGR

OSG

PHI1

PHI1L

OSB

OSR

PHICP

PHITGB

PHITGG

PHITGG

PHITGB

Loading...

Loading...