CHAPTER 5: SETPOINTS S5 OUTPUTS

745 TRANSFORMER PROTECTION SYSTEM – INSTRUCTION MANUAL 5–105

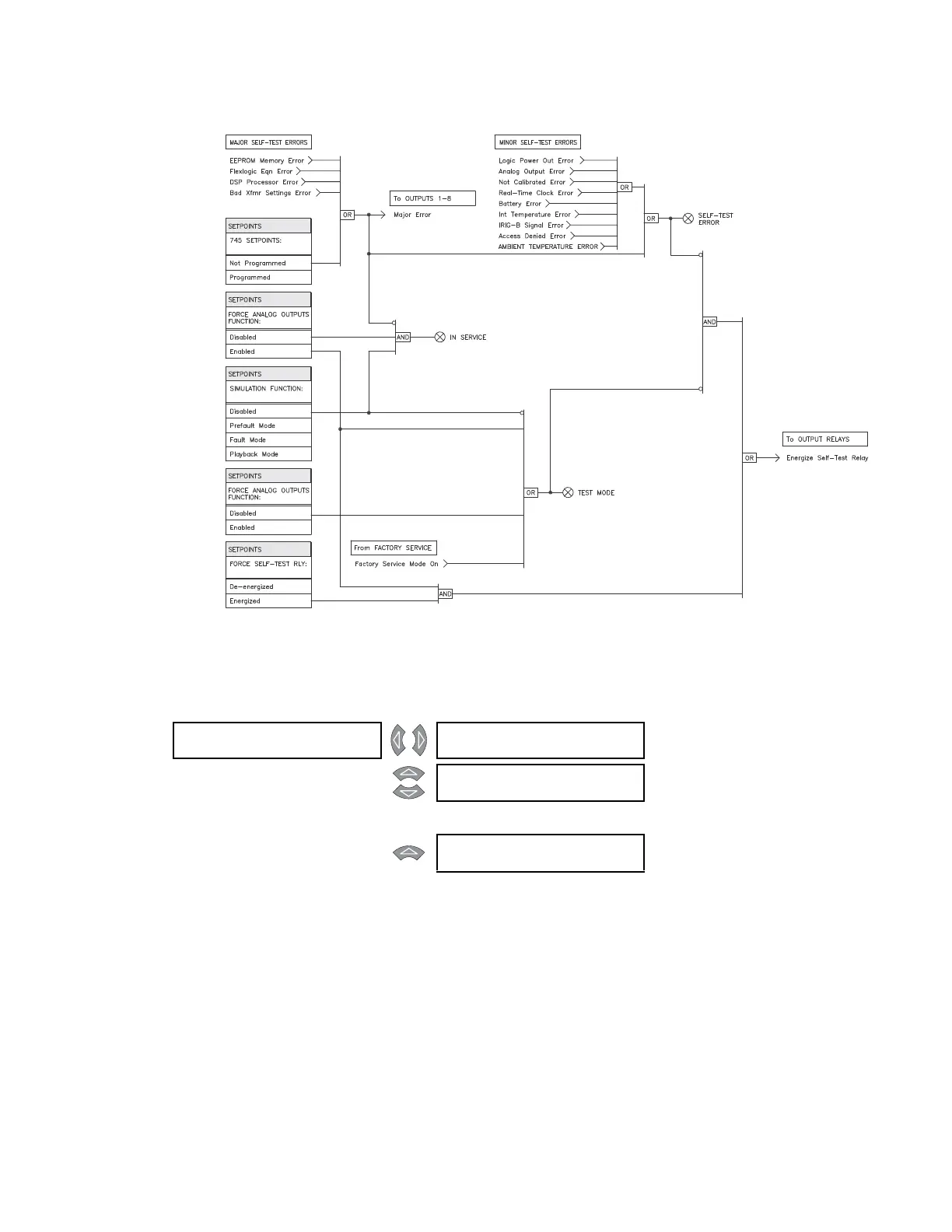

FIGURE 5–50: Self-test relays scheme logic

5.7.6 Trace Memory

PATH: SETPOINTS S5 OUTPUTS TRACE MEMORY

Trace memory is the oscillography feature of the 745. All system inputs are synchronously

digitized at a sampling rate of 64 times per power cycle. Upon occurrence of a user-

defined trigger condition, 32 cycles of oscillography waveforms are captured into trace

memory. The trigger condition is defined by a FlexLogic™ equation, and the number of

pre-trigger cycles of data captured is programmable.

This section contains the settings (including the FlexLogic™ equation) to configure trace

memory triggering.

• NO. OF PRE-TRIGGER CYCLES: Enter the number of cycles of data, of the 32 cycles of

waveform data to be captured, that are to be pre-trigger information.

TRACE MEMORY [] NO. OF PRE-TRIGGER

CYCLES: 12 cycles

Range: 1 to 31 in steps of 1

MESSAGE

TRACE TRIG FLEXLOGIC

01: Any Element PKP

Range: any FlexLogic™ input or gate

↓

MESSAGE

TRACE TRIG FLEXLOGIC

10: END

Range: any FlexLogic™ input or gate

Loading...

Loading...