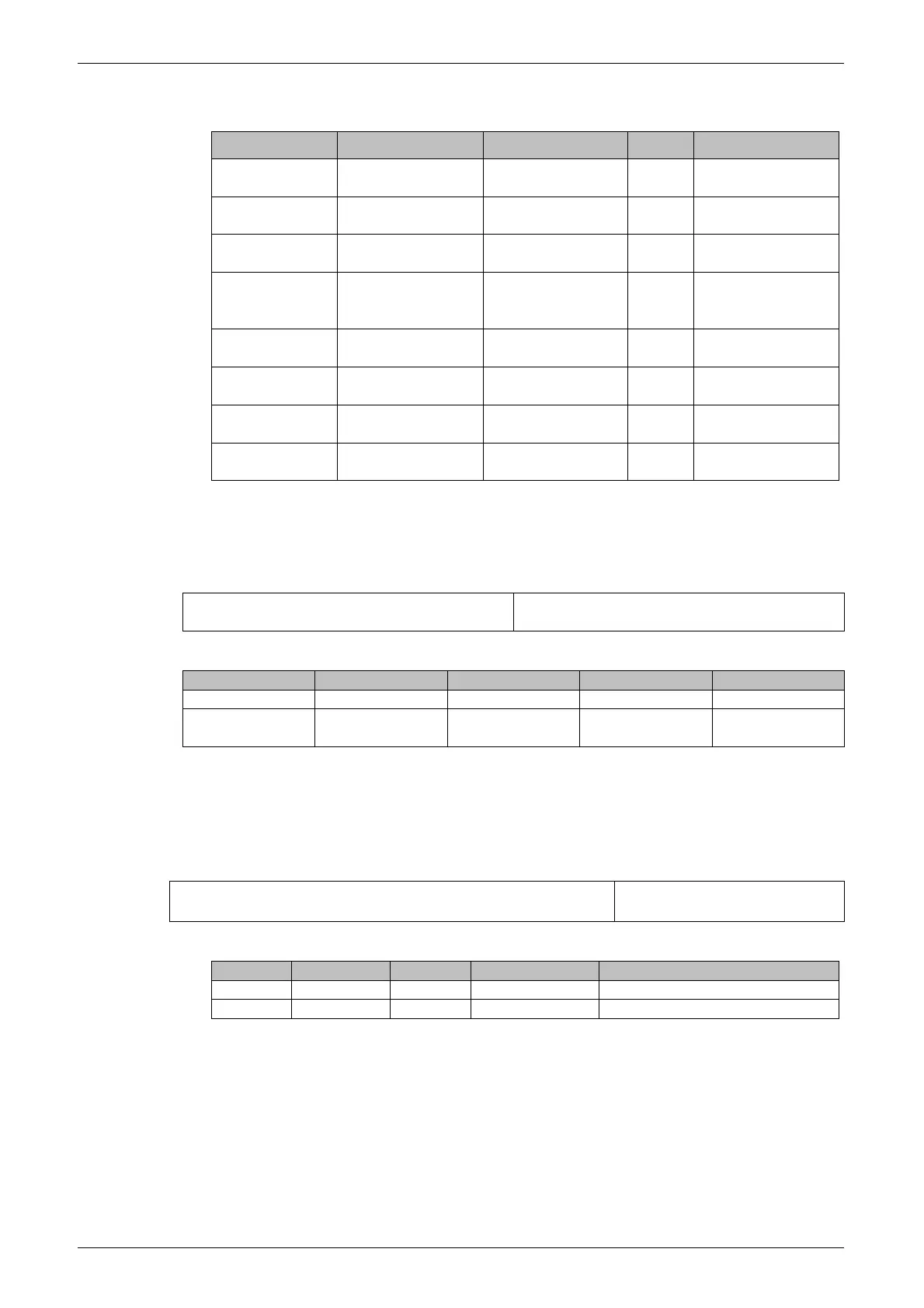

4.2Gowin UART Master IP Register

Table4-1 Gowin UART Master IP Register

Transmit Holding

Register

Interrupt Enable

Register

Interrupt

Identification

Register

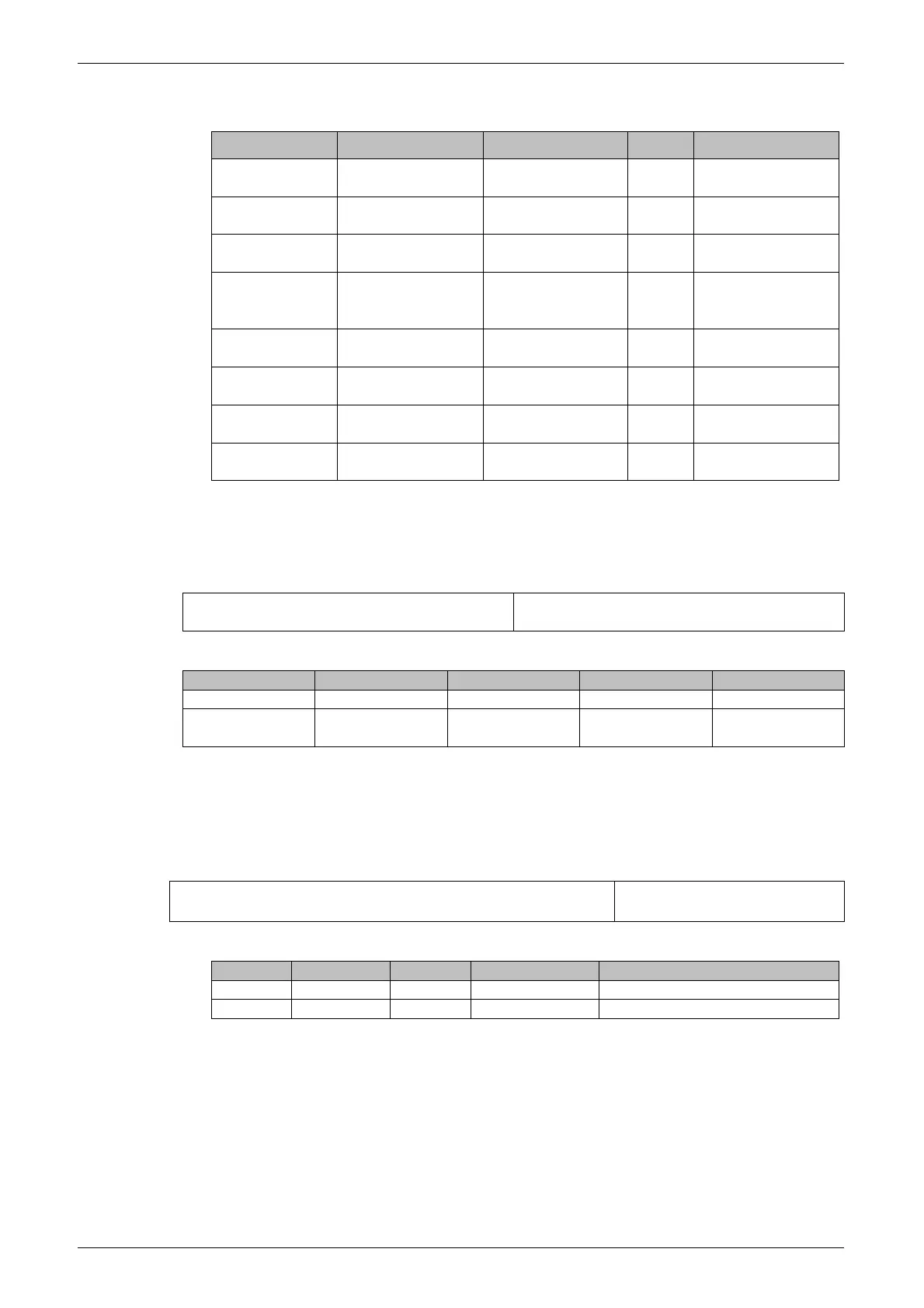

4.2.1 Receive Buffer Register (RBR)

The receive buffer register is shown in Figure4-2. The specific bit definition

of the register is shown in Table4-2.

Figure4-2 Receive Buffer Register

Table4-2 Receive Buffer Register Bit Definition

Cache the last

received byte

4.2.2 Transmit Holding Register (THR)

The transmit holding register is shown in Figure4-3. The transmit

holding register contains the data to be sent next time. The specific bit

definitions are shown in Table4-3.

Figure4-3 Transmit Holding Register

Table4-3 Transmit Holding Register Bit Definitions

4.2.3 Interrupt Enable Register (IER)

The interrupt enable register is shown in Figure4-4. The interrupt

enable register contains the bits that make the interrupt valid. The bit

definition is shown in Table4-4.

Loading...

Loading...