4.2Gowin UART Master IP Register

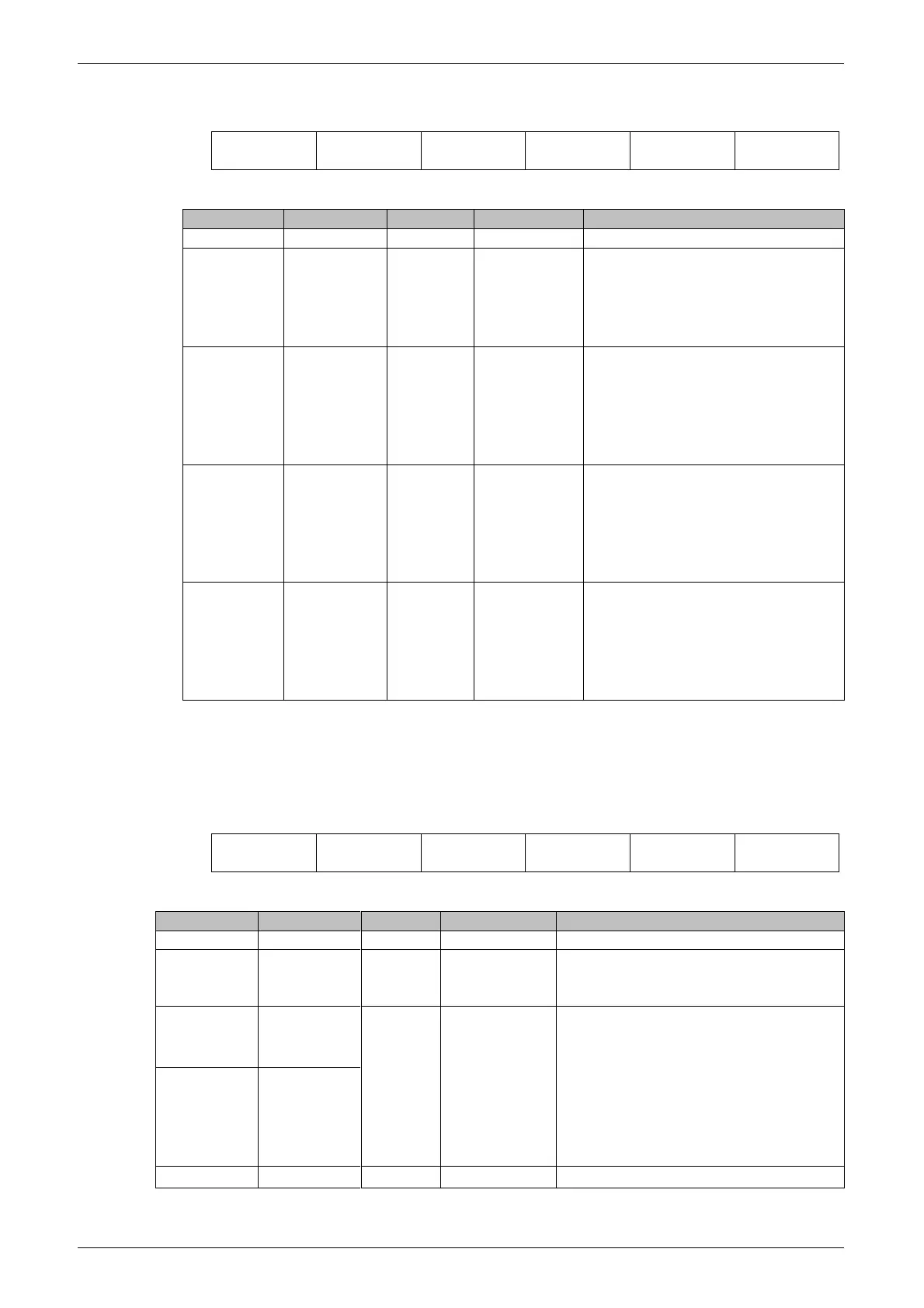

Figure4-4 Interrupt Enable Register

Table4-4 Interrupt Enable Register Bit Definition

Modem status interrupt enable

0:Disable Modem status

interrupt

1:Enable Modem status

interrupt

Receive line status interrupt

enable

0:Disable receive line status

interrupt

1:Enable Receive Line

Status Interrupt

Transmit Holding Register Empty

Interrupt Enable

0:Disable transmit hold

register empty interrupt

1:Enable transmit hold

register empty interrupt

Receive data valid interrupt

enable

0:Disable receive data valid

interrupt

1:Enable receive data valid

interrupt

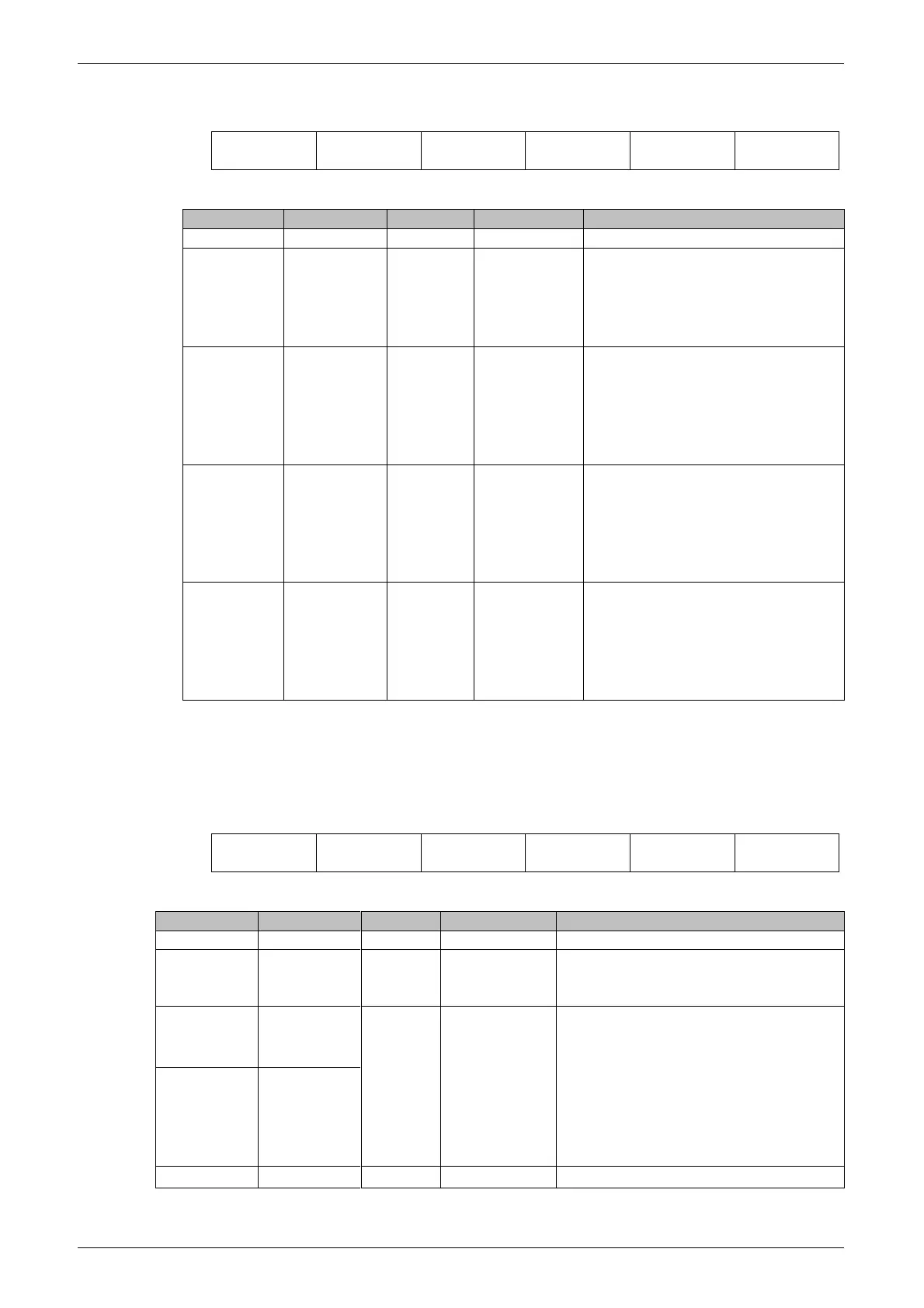

4.2.4 Interrupt Identification Register (IIR)

The interrupt identification register is shown in Figure4-5. The interrupt

identifier register contains the priority of the interrupt identifier. The bit definition

is shown in Table4-5.

Figure4-5 Interrupt Identification Register

Table4-5 Interrupt Identification Register Bit Definition

FIFO enable

0:16450 mode

1:16550 mode

Interrupt identifier

11:Receive line status (highest

priority)

10:Receive data available (Level

2)

01:Send Hold Register Empty

(Level 3)

00:Modem status (Level 4)

Loading...

Loading...