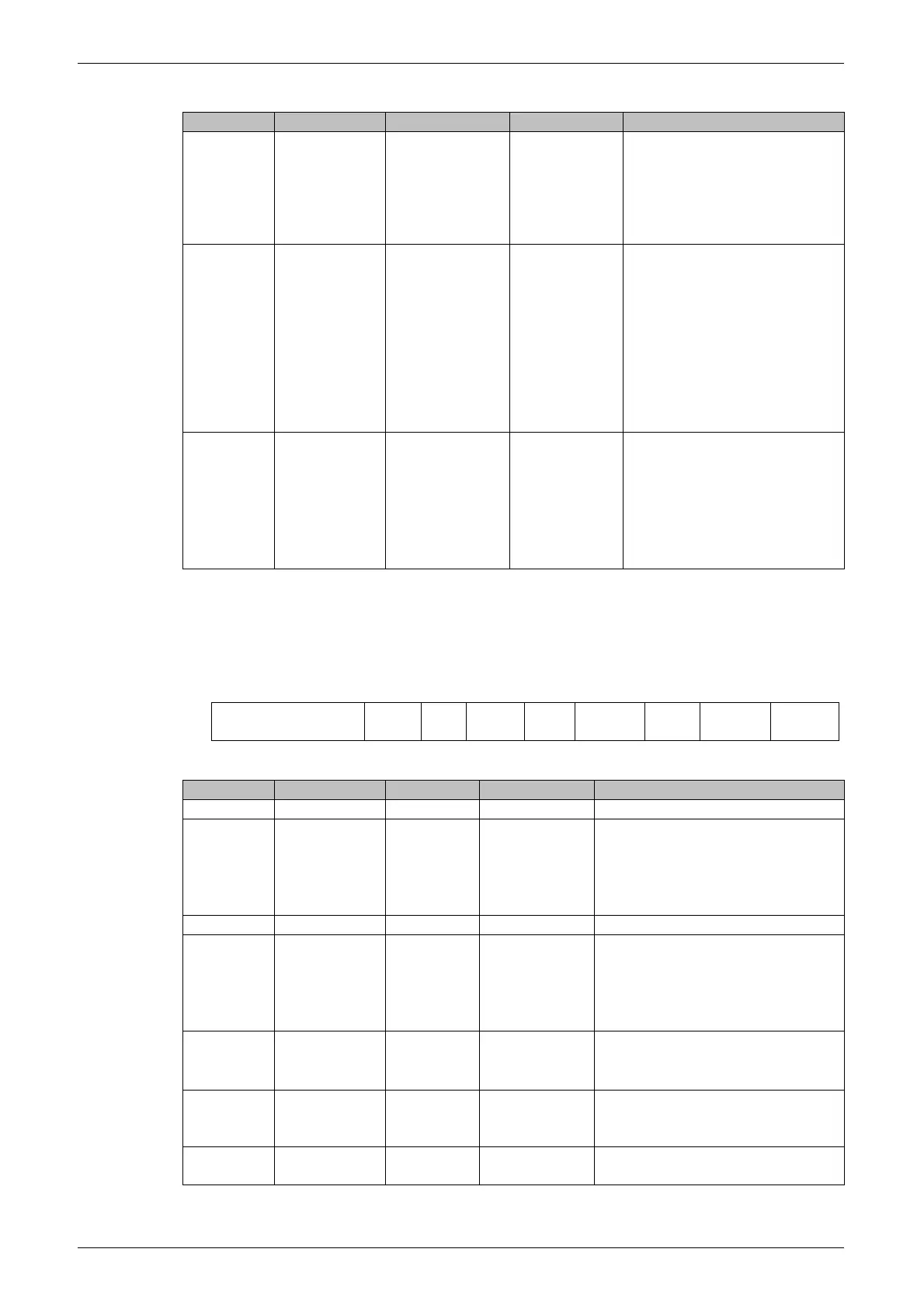

4.2Gowin UART Master IP Register

It means that the received

data does not have the

correct even or odd number,

which is inconsistent with

the setting by the check

selection bit.

Overflow error

The RBR was not read

before the next data

reception, thus destroying

the previous data. In FIFO

mode, the overflow error is

sent as the FIFO is full, and

the receive shift register has

completed the next data

reception.

Data is ready

0:All RBR and FIFO

have been read

1:The data has been

received and

transferred to the RBR

FIFO

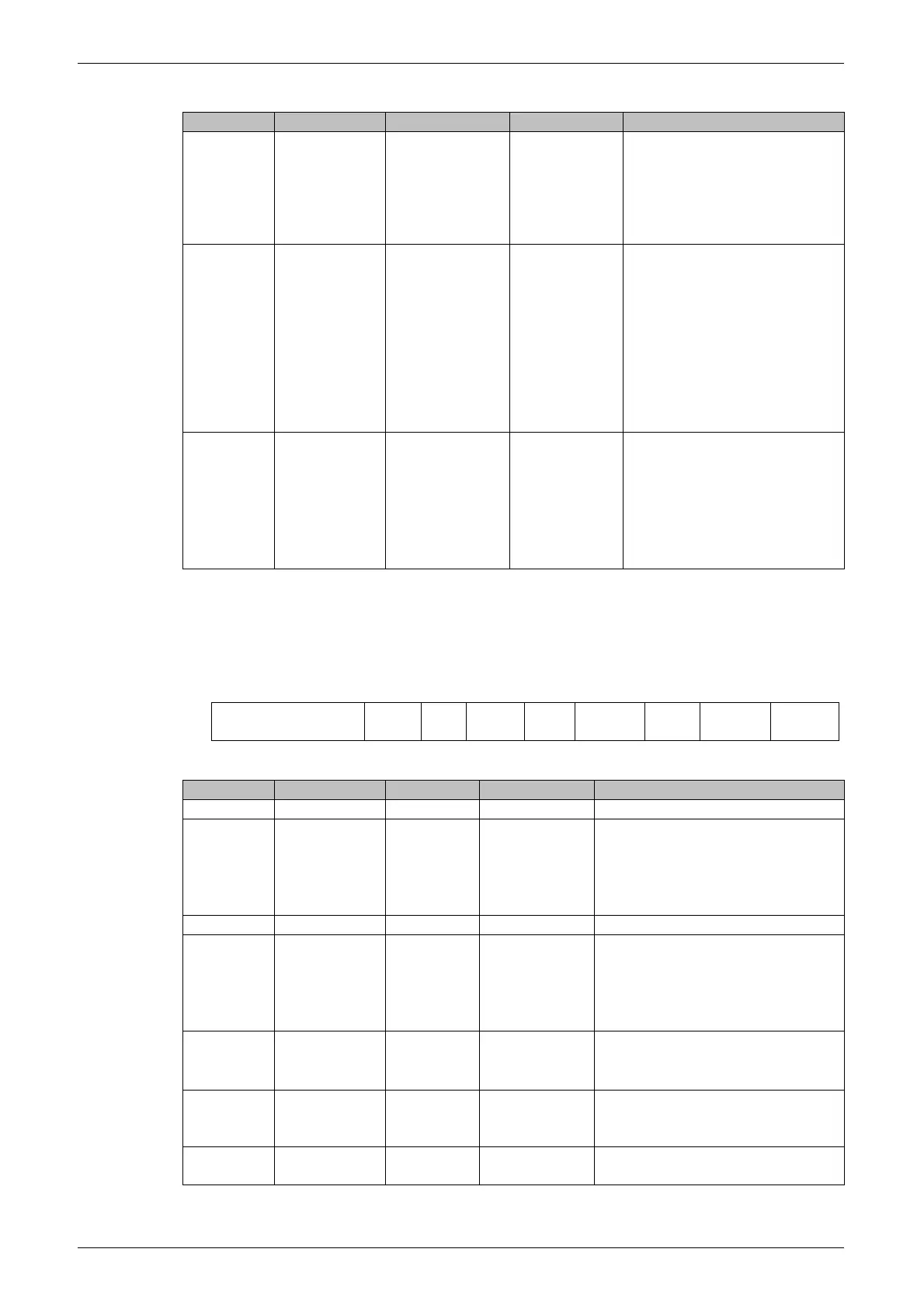

4.2.8 Modem Status Register (MSR)

The modem status register is shown in Figure4-9. The modem status

register contains the status of the current modem interface. The bit definitions

are shown in Table4-9.

Figure4-9 Modem Status Register

Table4-9 Modem Status Register

Data carrier detection (low

effective)

0:The data carrier has been

detected by the modem or data

device.

Data communication equipment

is ready (low effective)

0:The modem or data device is

ready to establish a connection

with the UART

Allow to send (low effective)

0:Modem or data device is

ready to exchange data

Delta Data Carrier Detect.

Change in DCDN after last MSR

read.

Trailing Edge Ring Indicator.

RIN has changed from a low to

Loading...

Loading...