8XC251SA, SB, SP, SQ USER’S MANUAL

6-12

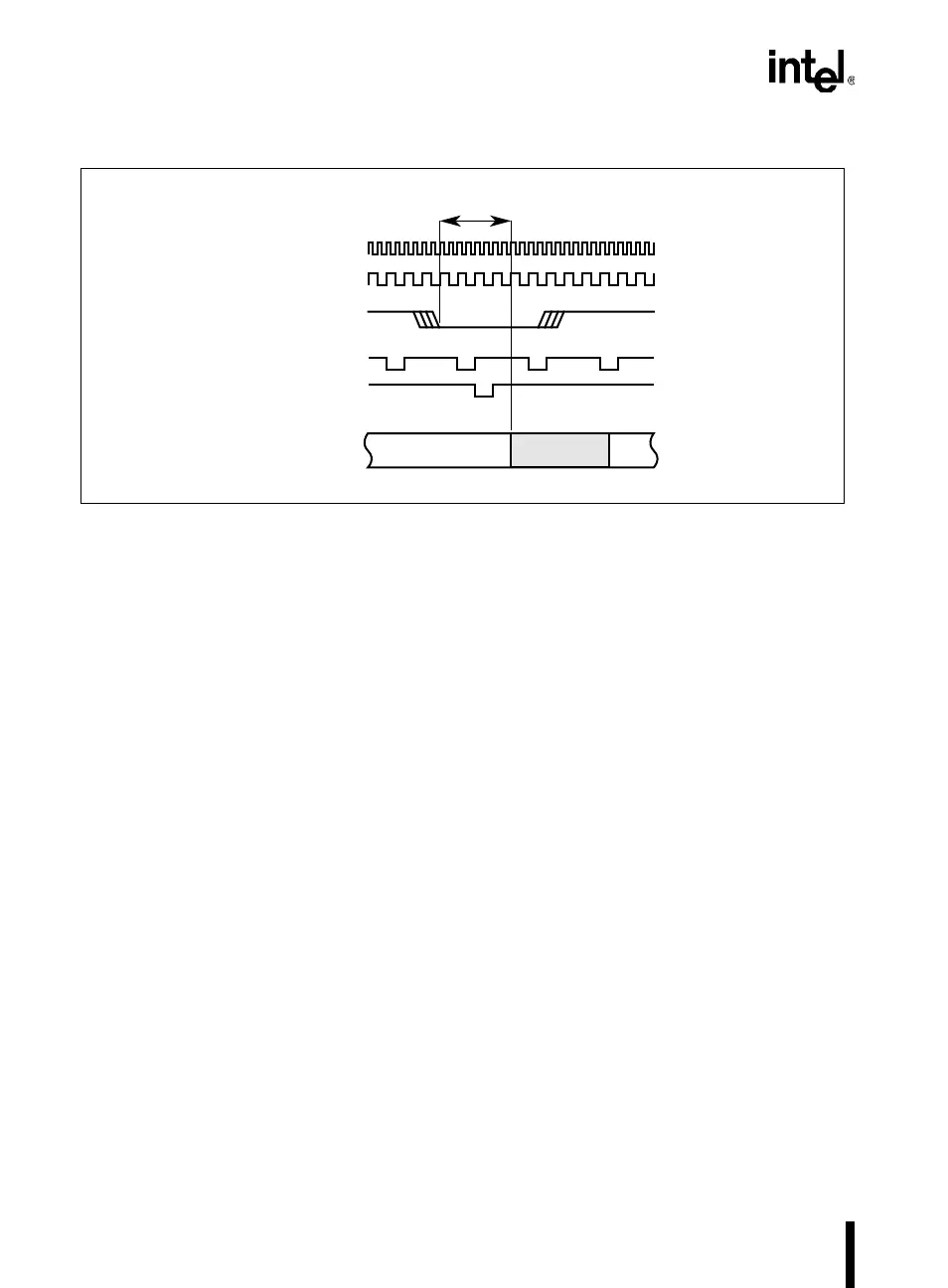

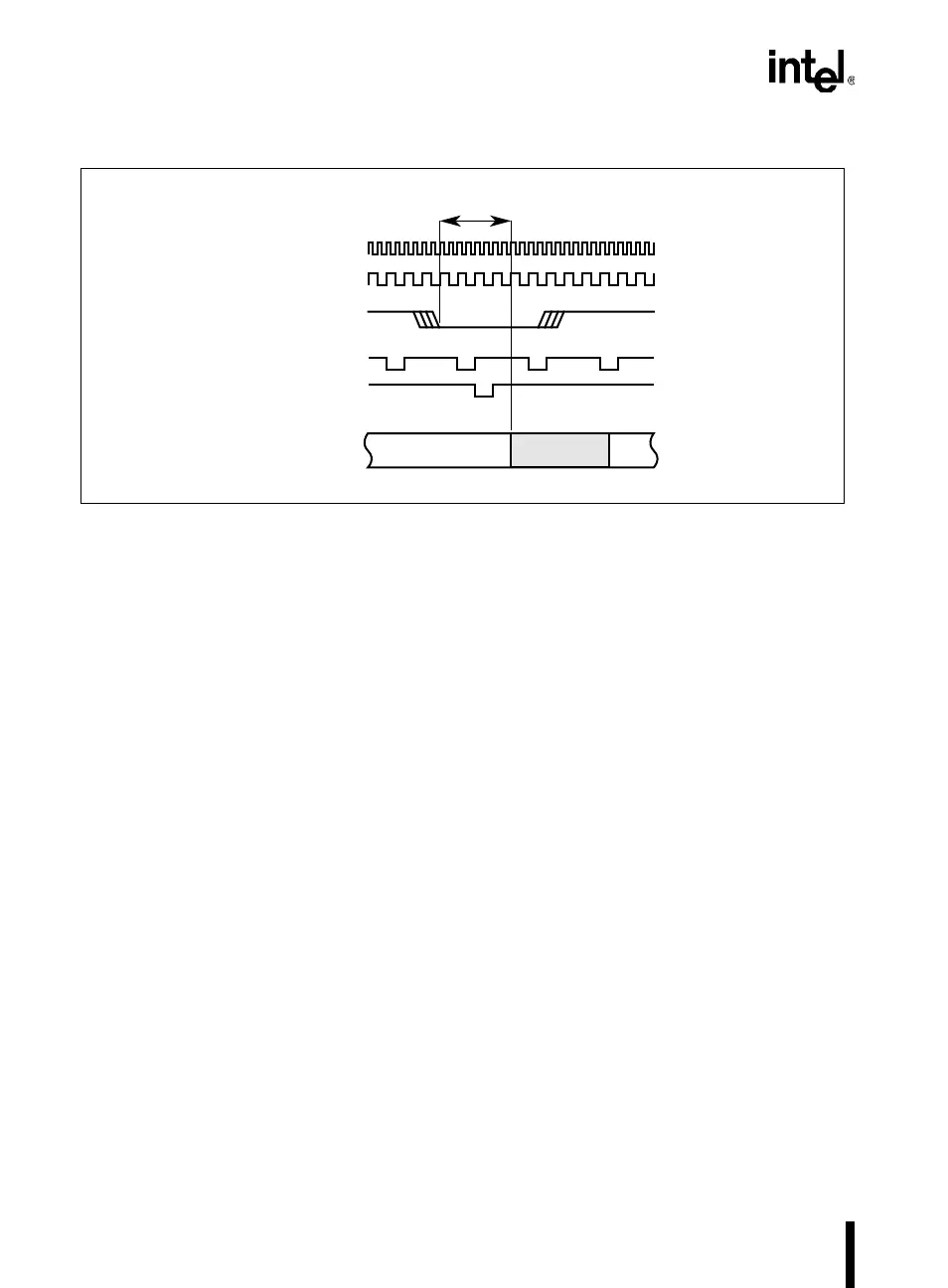

Figure 6-7. Response Time Example #2

6.7.2.2 Computation of Worst-case Latency With Variables

Worst-case latency calculations assume that the longest 8XC251Sx instruction used in the pro-

gram must fully execute prior to a context switch. The instruction execution time is reduced by

one state with the assumption the instruction state overlaps the request state (therefore, 16-bit

DIV is 21 state times - 1 = 20 states for latency calculations). The calculations add fixed and vari-

able interrupt times (see Table 6-6) to this instruction time to predict latency. The worst-case la-

tency (both fixed and variable times included) is expressed by a pseudo-formula:

OSC

State Time

INT0#

Sample INT0#

Response Time = 4

Ten State

Instruction

Request

Push PC

A4154-02

FIXED_TIME VARIABLES LONGEST_INSTRUCTION++ MAXIMUM LATENCY PREDICTION=

Loading...

Loading...