8XC251SA, SB, SP, SQ USER’S MANUAL

13-10

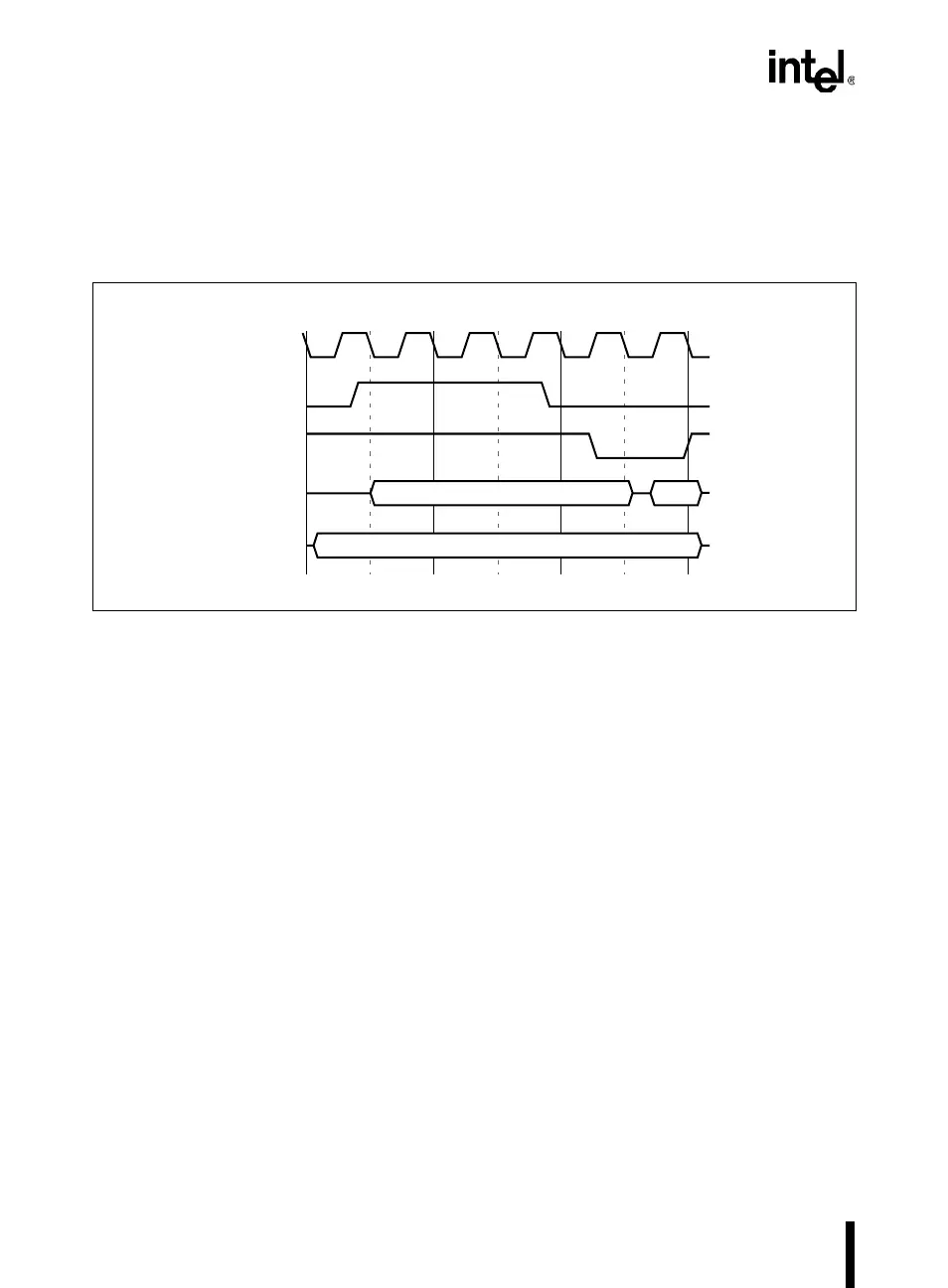

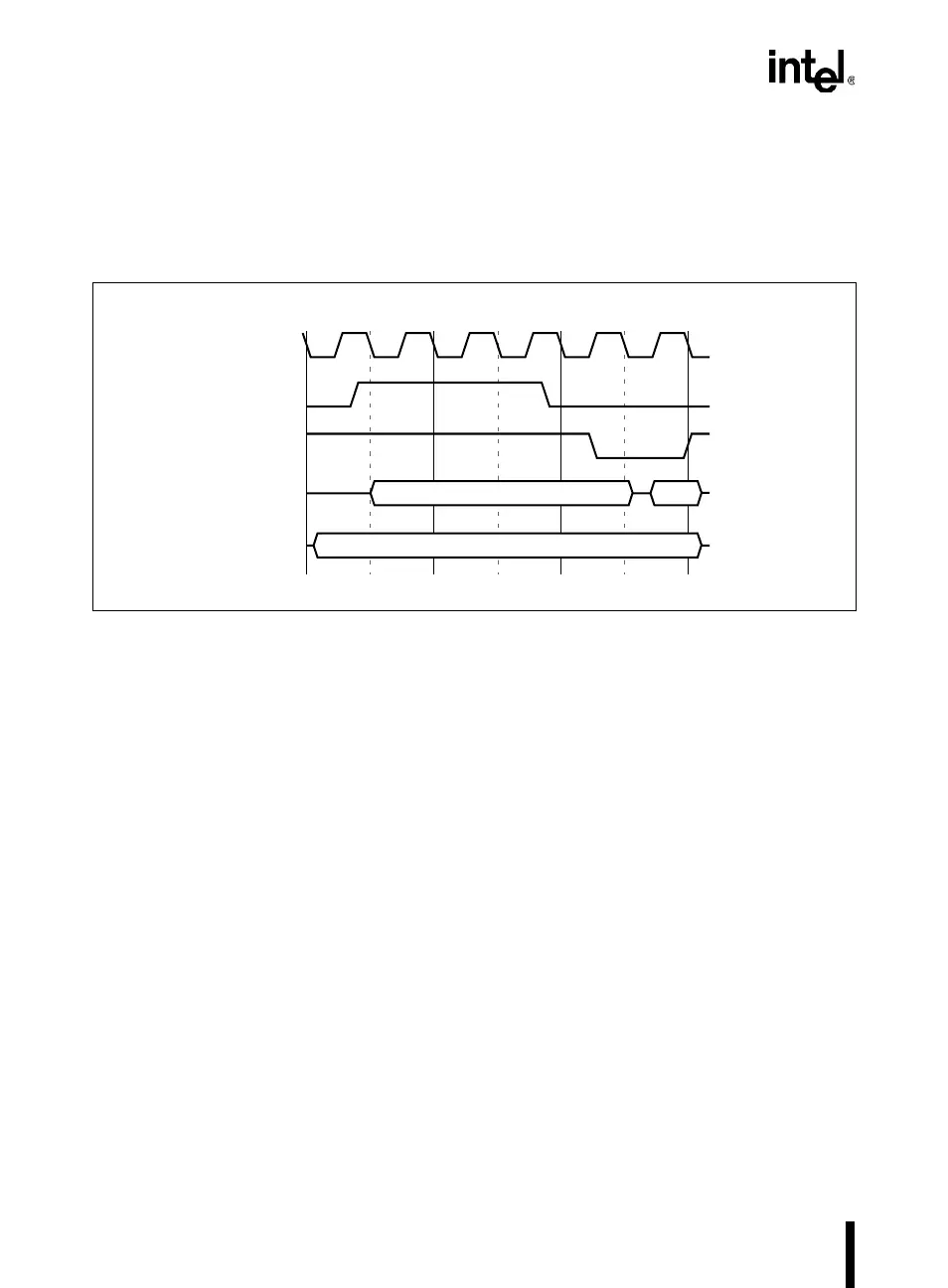

13.4.2 Extending ALE

Figure 13-10 shows the nonpage mode code fetch external bus cycle with ALE extended. The

wait state extends the bus cycle from two states to three. For read and write external bus cycles,

the extended ALE extends the bus cycle from three states to four.

Figure 13-10. External Code Fetch (Nonpage Mode, One ALE Wait State)

13.5 EXTERNAL BUS CYCLES WITH REAL-TIME WAIT STATES

In addition to fixed-length wait states such as RD#/WR#/PSEN# and ALE, the 8XC251SA, SB,

SP, SQ offers a real-time wait state. The programmer can dynamically adjust the delay of the real-

time wait state by means of registers.

There are two ways of using real-time wait states; the WAIT# pin used as an input bus control and

the WAIT# signal used in conjunction with the WCLK output signal. These two signals are en-

abled with the WCON special function register in the SFR space at S:0A7H. Refer to Figure

13-11.

P0

A17/A16/P2

ALE

RD#/PSEN#

State 1 State 2

XTAL

State 3

A2813-04

A7:0

D7:0

A15:8

Loading...

Loading...