8XC251SA, SB, SP, SQ USER’S MANUAL

8-2

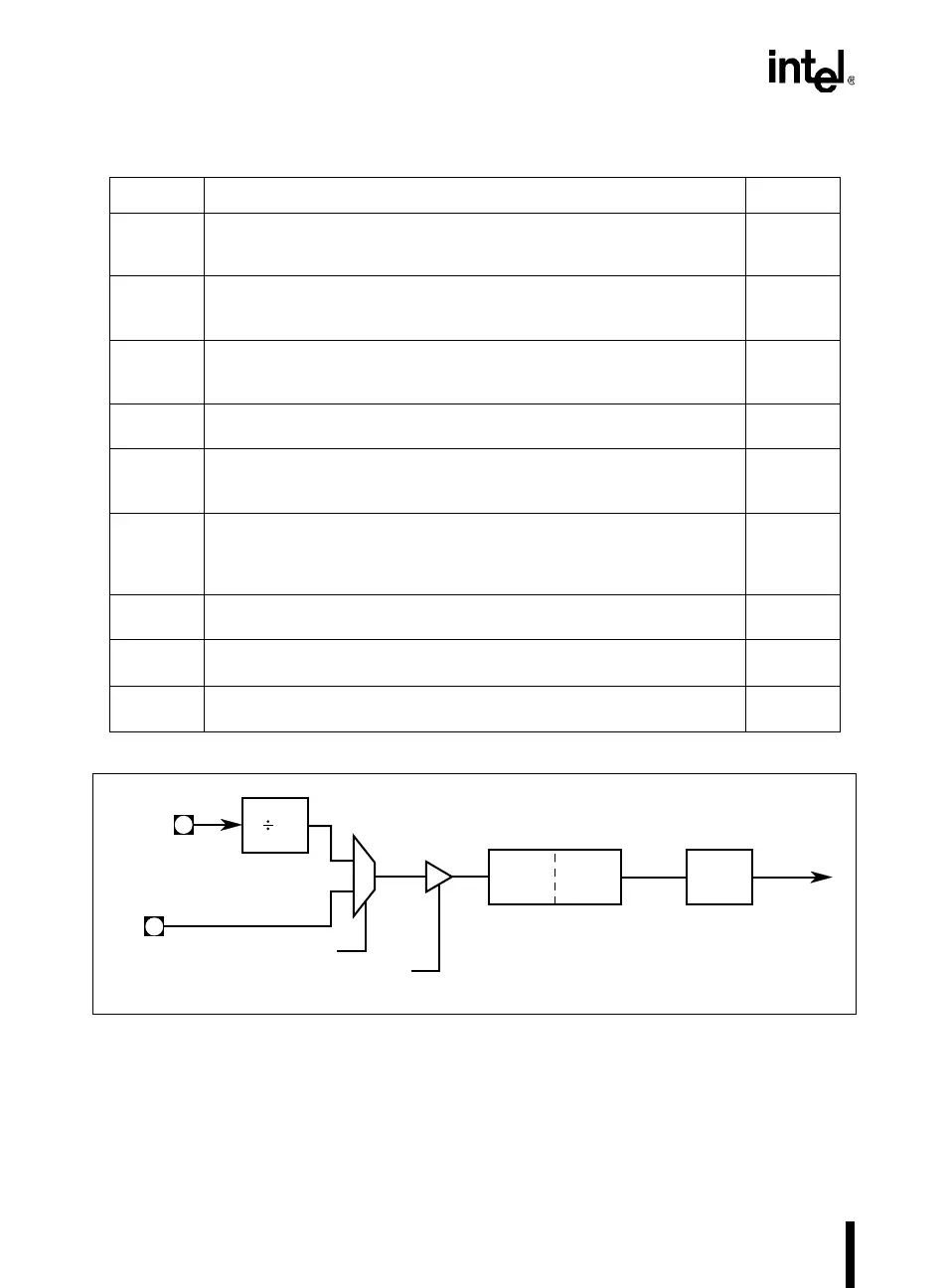

Figure 8-1. Basic Logic of the Timer/Counters

The C\Tx# control bit selects timer operation or counter operation by selecting the divided-down

system clock or external pin Tx as the source for the counted signal.

Table 8-1. Timer/Counter and Watchdog Timer SFRs

Mnemonic Description Address

TL0

TH0

Timer 0 Timer Registers. Used separately as 8-bit counters or in cascade

as a 16-bit counter. Counts an internal clock signal with frequency F

OSC

/12

(timer operation) or an external input (event counter operation).

S:8AH

S:8CH

TL1

TH1

Timer 1 Timer Registers. Used separately as 8-bit counters or in cascade

as a 16-bit counter. Counts an internal clock signal with frequency F

OSC

/12

(timer operation) or an external input (event counter operation).

S:8BH

S:8DH

TL2

TH2

Timer 2 Timer Registers. TL2 and TH2 connect in cascade to provide a

16-bit counter. Counts an internal clock signal with frequency F

OSC

/12

(timer operation) or an external input (event counter operation).

S:CCH

S:CDH

TCON Timer 0/1 Control Register. Contains the run control bits, overflow flags,

interrupt flags, and interrupt-type control bits for timer 0 and timer 1.

S:88H

TMOD Timer 0/1 Mode Control Register. Contains the mode select bits,

counter/timer select bits, and external control gate bits for timer 0 and

timer 1.

S:89H

T2CON Timer 2 Control Register. Contains the receive clock, transmit clock, and

capture/reload bits used to configure timer 2. Also contains the run control

bit, counter/timer select bit, overflow flag, external flag, and external enable

for timer 2.

S:C8H

T2MOD Timer 2 Mode Control Register. Contains the timer 2 output enable and

down count enable bits.

S:C9H

RCAP2L

RCAP2H

Timer 2 Reload/Capture Registers (RCAP2L, RCAP2H). Provide values

to and receive values from the timer registers (TL2,TH2).

S:CAH

S:CBH

WDTRST Watchdog Timer Reset Register (WDTRST). Used to reset and enable

the WDT.

S:A6H

A4121-02

TR

x

TL

x

(8 Bits)

TH

x

(8 Bits)

TF

x

Interrupt

Request

12

T

x

Overflow

x

= 0, 1, or 2

XTAL1

C/T

x

#

0

1

Loading...

Loading...