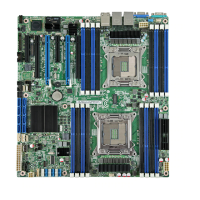

Intel® Server Board S2600CO Family TPS Functional Architecture Overview

Revision 1.4 31

Intel order number G42278-004

Integrated IOAPIC: Provides support for PCI Express* devices implementing legacy

interrupt messages without interrupt sharing

Non Transparent Bridge: PCI Express* non-transparent bridge (NTB) acts as a

gateway that enables high performance, low overhead communication between two

intelligent subsystems; the local and the remote subsystems. The NTB allows a local

processor to independently configure and control the local subsystem, provides isolation

of the local host memory domain from the remote host memory domain while enabling

status and data exchange between the two domains.

Intel

®

QuickData Technology: Used for efficient, high bandwidth data movement

between two locations in memory or from memory to I/O.

Dual GbDual Gb

Dual GbDual Gb

DMI2 PCIe Gen2 x4 (4GB/s)

PCIe Gen3 x16 (32GB/s)

PCIe Gen3 x4 (8GB/s)

PCIe Gen3 x4 (8GB/s)

P

C

I

e

G

e

n

2

x

4

(

4

G

B

/

s

)

Figure 14. Functional Block Diagram of Processor IIO Sub-system

The following sub-sections will describe the server board features that are directly supported by

the processor IIO module. These include the PCI Card Slots, Network Interface, and connectors

for the optional SAS Module. Features and functions of the Intel

®

C600 Series chipset will be

described in its own dedicated section.

Loading...

Loading...