CrossLink-NX Evaluation Board

User Guide

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

20 FPGA-EB-02028-1.3

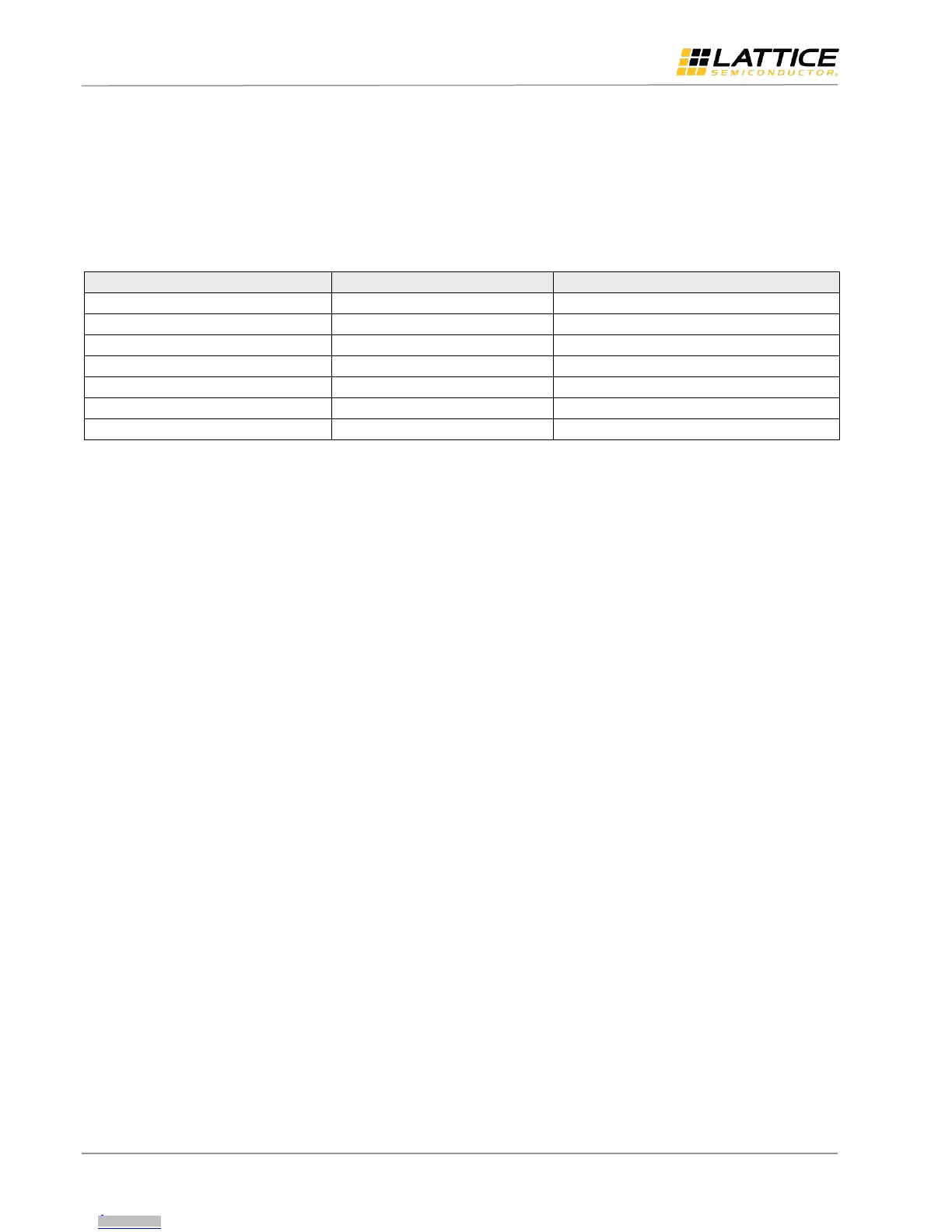

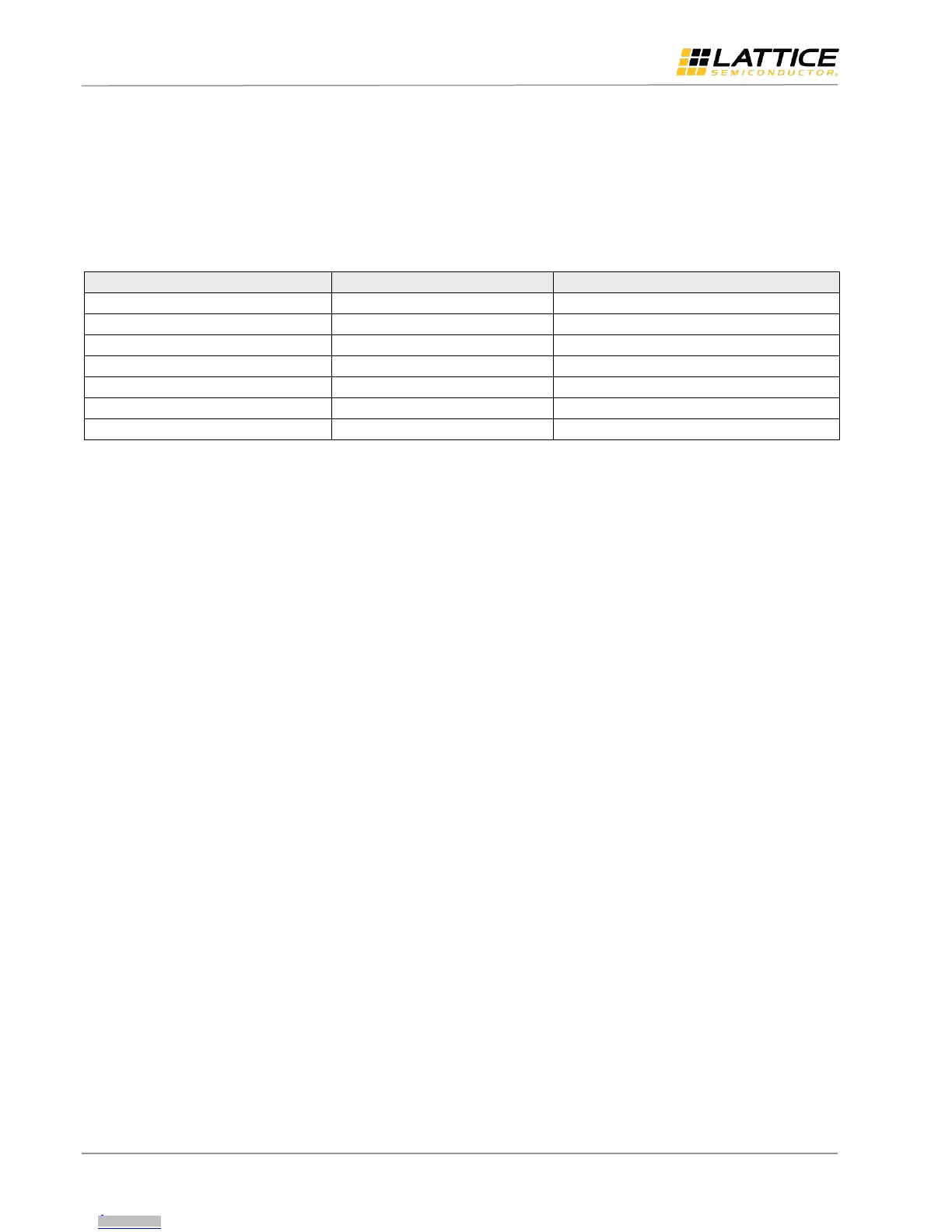

6.3. SPI Topology

6.3.1. SPI Configuration

One of the major functions of SPI connections on the board is to support CrossLink-NX configuration from the SPI Flash

or the Parallel Configuration Header. The CrossLink-NX Evaluation Board can support both Master SPI (MSPI) and Slave

SPI (SSPI) modes for CrossLink-NX configuration.

Table 6.2. CrossLink-NX SPI Connections

Parallel Configuration Header Pin

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.

Loading...

Loading...