32

3.4 Chipset Features Setup

This section allows you to configure the system based on the specific features of

the installed chipset. This chipset manages bus speeds and access to system

memory resources, such as DRAM and the external cache. It also coordinates

communications between the conventional ISA bus and the PCI bus. It must be

stated that these items should never need to be altered. The default settings have

been chosen because they provide the best operating conditions for your system.

The only time you might consider making any changes would be if you

discovered that data was being lost while using your system.

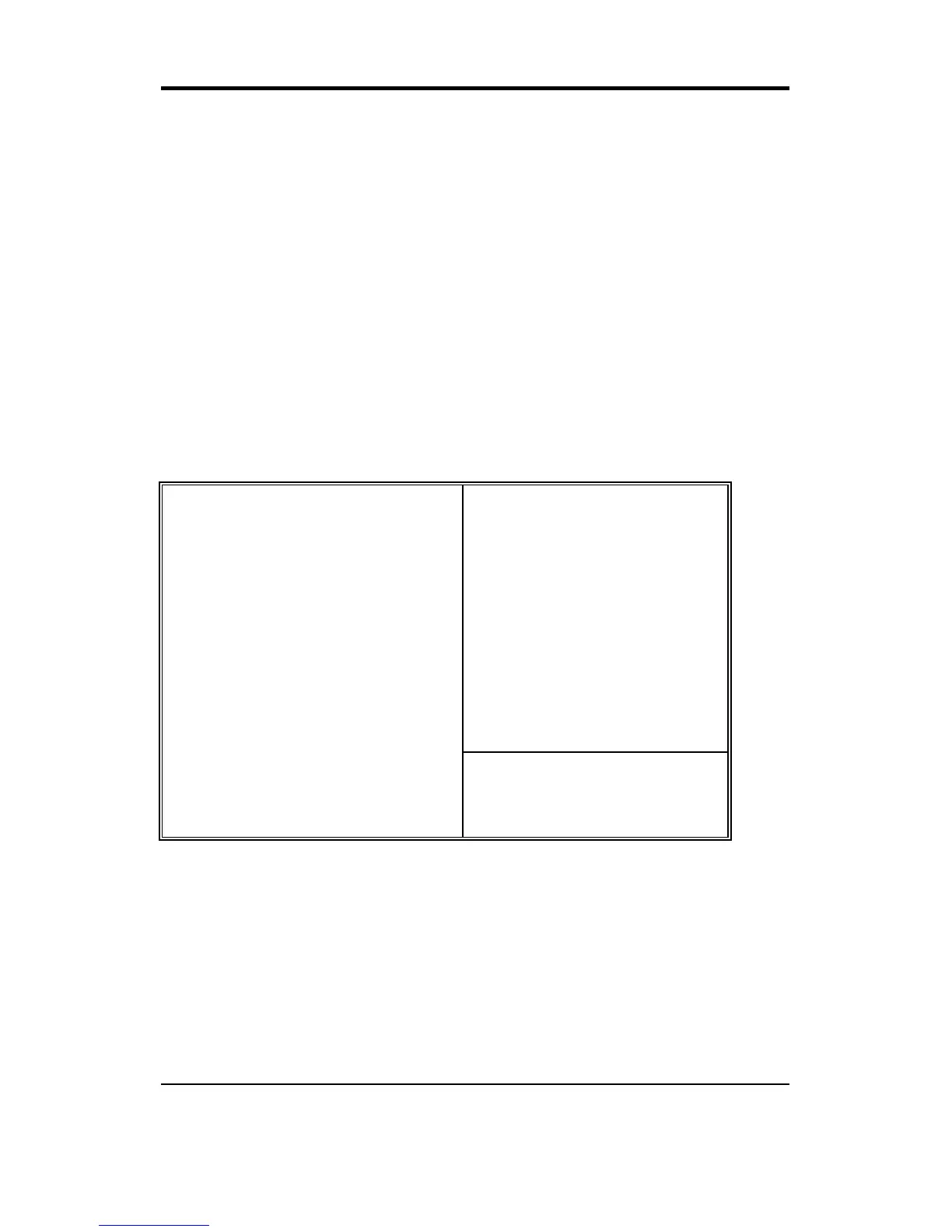

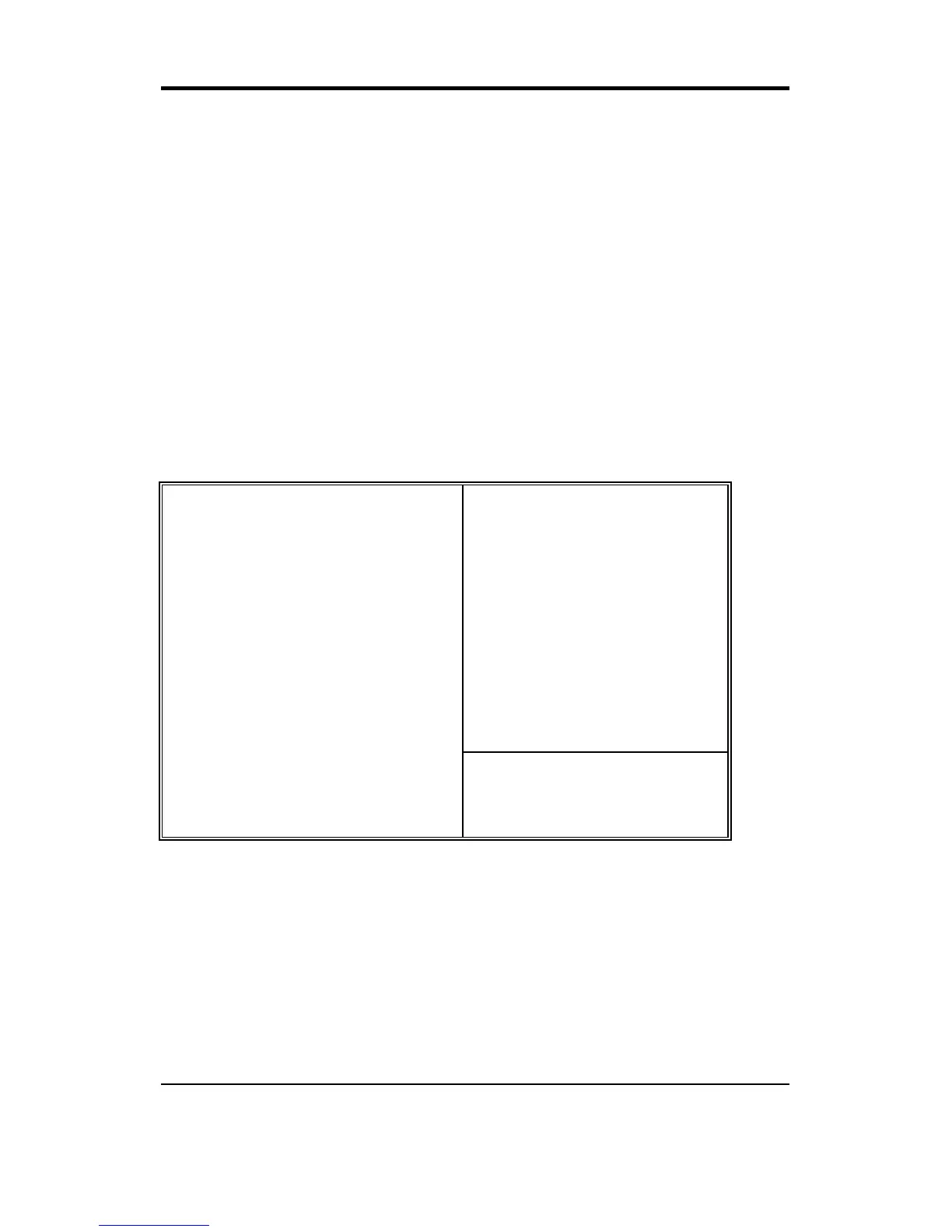

Figure 3.4 CHIPSET FEATURES SETUP SCREEN

ROM PCI / ISA BIOS (2A5LEV5B)

CHIPSET FEATURES SETUP

AWARD SOFTWARE, INC.

Bank 0/1 DRAM Timing : 70ns Auto Detect DIMM/PCI Clk : Enabled

Bank 2/3 DRAM Timing : 70ns Spread Spectrum Modulated : Disabled

Bank 4/5 DRAM Timing : 70ns CPU Warning Temperature : Disabled

SDRAM Cycle Length : 3 Current System Temp. : 26¢XC/78¢X

F

DRAM Read Pipeline : Enabled Current CPU Temperature : 41¢XC/105¢X

F

Sustained 3T Write : Enabled Current Power Temperature : 34¢XC/93¢X

F

Cache Rd+CPU Wt Pipeline : Enabled Current PowerFAN Speed : 0 RPM

Read Around Write : Enabled Current ChassisFAN Speed : 0 RPM

Cache Timing : Fast Current CPUFAN Speed : 0 RPM

Video BIOS Cacheable : Enabled

System BIOS Cacheable : Enabled Vcore(V): 2.89V

Memory Hole At 15Mb Addr : Disabled 3.3 V : 3.29V Vtt(V) : 3.37V

AGP Aperture Size : 256M +12V : 12.03V +5V : 4.89V

- 5V : - 5.09V -12V : -12.04V

On Chip USB : Disabled

ESC : Quit ↑ ↓ → ←: Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift) F2 : Color

F6 : Load BIOS Defaults

F7 : Load Setup Defaults

3.4.1 Bank 0/1 & 2/3 & 4/5 DRAM Timing (70ns)

This value in this field is set by the system board manufacturer, depending

on whether the board has paged DRAMs or EDO (extended data output)

DRAMs.

3.4.2 SDRAM Cycle Length (3)

This field sets the CAS latency timing.

Loading...

Loading...