Page 4

1. Overview

67f o5002, 92. guA10 . 1. veR

1010 - 7210B30JER

)B78 / C23M, A78 /C23M, 78 / C23M(puo rG78 / C23M

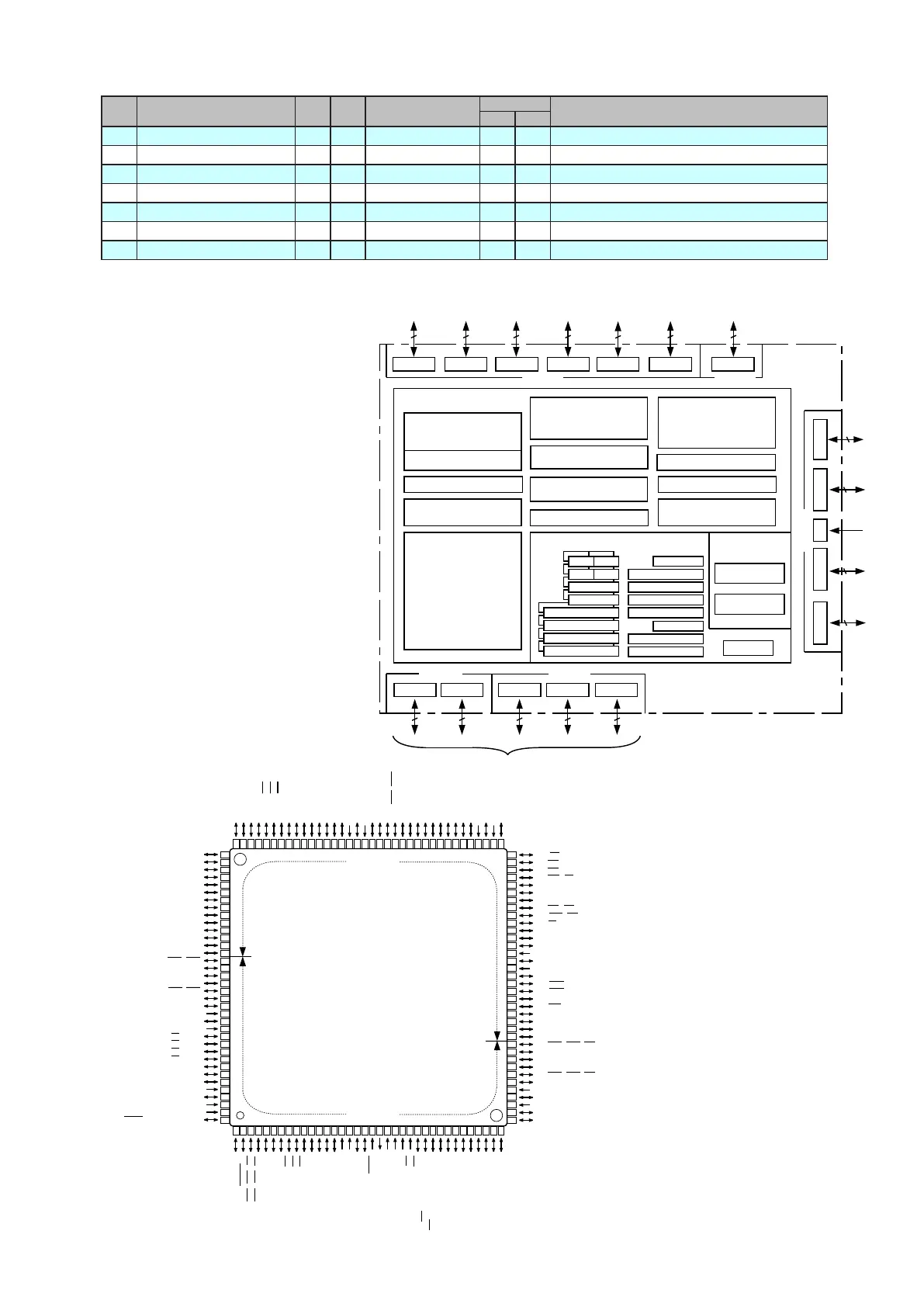

1.3 Block Diagram

Figure 1.1 shows a block diagram of the M32C/87 group (M32C/87, M32C/87A, M32C/87B) microcomputer.

Figure 1.1 M32C/87 Group (M32C/87, M32C/87A, M32C/87B) Block Diagram

Port P0 Port P1 Port P2 Port P3 Port P4 Port P5 Port P6

Port P7

Port P14 Port P15 Port P11 Port P12

Port P10Port P9Port P8

P8

5

Port P13

R0H R0L

R1H R1L

R2

R3

A0

A1

FB

SB

NOTES:

1. Ports P11 to P15 are provided in the 144-pin package only.

2. Included in the 144-pin package only. 26 inputs maximum in the 100-pin package.

3. 6 channes available in the 100-pin package.

4. 10 channes available in the 100-pin package.

5. 1 channel is included in M32C/87A. No channel is included in M32C/87B.

FLG

INTB

ISP

USP

PC

SVF

SVP

VCT

Multiplier

M32C/80 series CPU Core

Clock Generation Circuit

X

IN

- X

OUT

X

CIN

- X

COUT

On-chip Oscillator

PLL Frequency Synthesizer

A/D Converter:

1 circuit

Standard: 10 inputs

Maximum: 34 inputs

(2)

UART/Clock Synchronous Serial I/O:

7 channels

(3)

CRC Calculation Circuit (CCITT):

X

16

+X

12

+X

5

+1

X/Y Converter:

16 bits x 16 bits

D/A Converter:

8 bits x 2 circuits

Peripheral Functions

<

V

CC2><

V

CC1>

<

V

CC1>

ROM

RAM

Memory

<

V

CC1>

<

V

CC2>

78588

(Note 1)

8

8

7

8888888

8

DMACII

DMAC

Watchdog Timer (15 bits)

CAN Module: 2 channels

(5)

Intelligent I/O

Time Measurement: 8 channels

Wave Generating: 16 channels

(4)

Communication Functions:

Clock Synchronous Serial I/O,

UART,

HDLC Data Processing,

IEBus,

Clock Synchronous Variable

Length Serial I/O

Timer (16 bits)

Timer A: 5 channels

Timer B: 6 channels

Three-Phase Motor Control Circuit

Page 7

1. Overview

67f o5002, 92. guA10 . 1. veR

1010 - 7210B30JER

)B78 / C23M, A78 /C23M, 78 / C23M(puo rG78 / C23M

P4

4

/ CS3 / A

20

P4

5

/ CS2 / A

21

P4

6

/ CS1 / A

22

P4

7

/ CS0 / A

23

P12

5

P12

6

P12

7

P5

0

/ WRL / WR

P5

1

/ WRH / BHE

P5

2

/ RD

P5

3

/ CLK

OUT

/ BCLK / ALE

P13

0

/ OUTC2

4

P13

1

/ OUTC2

5

V

CC2

P13

2

/ OUTC2

6

V

SS

P13

3

/ OUTC2

3

P5

4

/ HLDA / ALE

P5

5

/ HOLD

P5

6

/ ALE

P5

7

/ RDY

P13

4

/ OUTC2

0

/ ISTxD2 / IE

OUT

P13

5

/ OUTC2

2

/ ISRxD2 / IE

IN

P13

6

/ OUTC2

1

/ ISCLK2

P13

7

/ OUTC2

7

P6

0

/ CTS0 / RTS0 / SS0 / RTP0

0

P6

1

/ CLK0 / RTP0

1

P6

2

/ RxD0 / SCL0 / STxD0 / IrDA

IN

P6

3

/ TxD0 / SDA0 / SRxD0 / IrDA

OUT

P6

4

/ CTS1 / RTS1 / SS1 / OUTC2

1

/ ISCLK2

P6

5

/ CLK1

V

SS

P6

6

/ RxD1 / SCL1 / STxD1

V

CC1

P6

7

/ TxD1 / SDA1 / SRxD1

P7

0

(11,14)

P9

6

(1,15)

P9

5

/ ANEX0 / CLK4 / CAN1

IN

/ CAN1WU

(15)

P9

4

/ DA1 / TB4

IN

/ CTS4 / RTS4 / SS4

P9

3

/ DA0 / TB3

IN

/ CTS3 / RTS3 / SS3

P9

2

(2)

P9

1

(3)

P9

0

/ TB0

IN

/ CLK3

P14

6

/ INT8

P14

5

/ INT7

P14

4

/ INT6

P14

3

/ INPC1

7

/ OUTC1

7

P14

2

/ INPC1

6

/ OUTC1

6

P14

1

/ INPC1

5

/ OUTC1

5

P14

0

/ INPC1

4

/ OUTC1

4

BYTE

CNV

SS

P8

7

/ X

CIN

P8

6

/ X

COUT

RESET

X

OUT

V

SS

X

IN

V

CC1

P8

5

/ NMI

P8

4

/ INT2

P8

3

/ INT1 / CAN1

IN

/ CAN0

IN

(15)

P8

2

/ INT0 / CAN1

OUT

/ CAN0

OUT

(15)

P8

1

(4)

P8

0

/ TA4

OUT

/ U / ISRxD0 / RxD5

P7

7

(5,15)

P7

6

(6,15)

P7

5

(7)

P7

4

(8)

P7

3

(9)

P7

2

/ TA1

OUT

/ V / CLK2

P7

1

(10,14)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

50

49

48

47

46

45

44

43

42

41

40

39

38

37

56

55

54

53

52

51

62

61

60

59

58

57

68

67

66

65

64

63

72

71

70

69

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

131

132

133

134

135

136

137

138

139

140

141

142

143

144

125

126

127

128

129

130

11 9

120

121

122

123

124

11 3

11 4

11 5

11 6

11 7

11 8

109

11 0

111

11 2

M32C/87 Group

(M32C/87,M32C/87A,M32C/87B)

P1

1

/ D

9

P1

2

/ D

10

P1

3

/ D

11

P1

4

/ D

12

P1

5

/ D

13

/ INT3

P1

6

/ D

14

/ INT4

P1

7

/ D

15

/ INT5

P2

0

/ A

0

( / D

0

) / AN2

0

P2

1

/ A

1

( / D

1

) / AN2

1

P2

2

/ A

2

( / D

2

) / AN2

2

P2

3

/ A

3

( / D

3

) / AN2

3

P2

4

/ A

4

( / D

4

) / AN2

4

P2

5

/ A

5

( / D

5

) / AN2

5

P2

6

/ A

6

( / D

6

) / AN2

6

P2

7

/ A

7

( / D

7

) / AN2

7

V

SS

P3

0

/ A

8

( / D

8

)

V

CC2

P12

0

/ TxD6

P12

1

/ CLK6

P12

2

/ RxD6

P12

3

/ CTS6 / RTS6

P12

4

P3

1

/ A

9

( / D

9

)

P3

2

/ A

10

( / D

10

)

P3

3

/ A

11

( / D

11

)

P3

4

/ A

12

( / D

12

)

P3

5

/ A

13

( / D

13

)

P3

6

/ A

14

( / D

14

)

P3

7

/ A

15

( / D

15

)

P4

0

/ A

16

P4

1

/ A

17

V

SS

P4

2

/ A

18

V

CC2

P4

3

/ A

19

P1

0

/ D

8

P0

7

/ D

7

/ AN0

7

P0

6

/ D

6

/ AN0

6

P0

5

/ D

5

/ AN0

5

P0

4

/ D

4

/ AN0

4

P11

4

P11

3

/ INPC1

3

/ OUTC1

3

P11

2

(12)

P11

1

/ INPC1

1

/ OUTC1

1

/ ISCLK1

P11

0

(13)

P0

3

/ D

3

/ AN0

3

P0

2

/ D

2

/ AN0

2

P0

1

/ D

1

/ AN0

1

P0

0

/ D

0

/ AN0

0

P15

7

/ AN15

7

/ CTS6 / RTS6

P15

6

/ AN15

6

/ CLK6

P15

5

/ AN15

5

/ RxD6

P15

4

/ AN15

4

/ TxD6

P15

3

/ AN15

3

/ CTS5 / RTS5

P15

2

/ AN15

2

/ ISRxD0 / RxD5

P15

1

/ AN15

1

/ ISCLK0 / CLK5

V

SS

P15

0

/ AN15

0

/ ISTxD0 / TxD5

V

CC1

P10

7

/ AN

7

/ KI

3

/ RTP3

3

P10

6

/ AN

6

/ KI

2

/ RTP3

2

P10

5

/ AN

5

/ KI

1

/ RTP3

1

P10

4

/ AN

4

/ KI

0

/ RTP3

0

P10

3

/ AN

3

/ RTP1

3

P10

2

/ AN

2

/ RTP1

2

P10

1

/ AN

1

/ RTP1

1

AV

SS

P10

0

/ AN

0

/ RTP1

0

V

REF

AV

CC

P9

7

/ ADTRG / RxD4 / SCL4 / STxD4

<

VCC2

>

<

VCC1

>

NOTES:

1. P9

6

/ ANEX1 / TxD4 / SDA4 / SRxD4 / CAN1

OUT

2. P9

2

/ TB2

IN

/ TxD3 / SDA3 / SRxD3 / OUTC2

0

/ IE

OUT

/ ISTxD2

3. P9

1

/ TB1

IN

/ RxD3 / SCL3 / STxD3 / IE

IN

/ ISRxD2

4. P8

1

/ TA4

IN

/ U / INPC1

5

/ OUTC1

5

/ CTS5 / RTS5 / RTP2

3

5. P7

7

/ TA3

IN

/ CAN0

IN

/ INPC1

4

/ OUTC1

4

/ ISCLK0 / CLK5 / RTP2

2

6. P7

6

/ TA3

OUT

/ CAN0

OUT

/ INPC1

3

/ OUTC1

3

/ ISTxD0 / TxD5

7. P7

5

/ TA2

IN

/ W / INPC1

2

/ OUTC1

2

/ ISRxD1 / RTP2

1

8. P7

4

/ TA2

OUT

/ W / INPC11 / OUTC11 / ISCLK1 / RTP20

9. P7

3

/ TA1

IN

/ V / CTS2 / RTS2 / SS2 / INPC1

0

/ OUTC1

0

/ ISTxD1

10. P7

1

/ TA0

IN

/ TB5

IN

/ RxD2 / SCL2 / STxD2 / INPC1

7

/ OUTC1

7

/ OUTC2

2

/ ISRxD2 / IE

IN

/ RTP0

3

11. P7

0

/ TA0

OUT

/ TxD2 / SDA2 / SRxD2 / INPC1

6

/ OUTC1

6

/ OUTC2

0

/ ISTxD2 / IE

OUT

/ RTP0

2

12. P11

2

/ INPC1

2

/ OUTC1

2

/ ISRxD1

13. P11

0

/ INPC1

0

/ OUTC1

0

/ ISTxD1

14. P7

0

and P7

1

are ports for the N-channel open drain output.

15. The CAN pin cannot be used in M32C/87B. Only CAN 0 pin can be used in 32C/87A.

PLQP0144KA-A

(144P6Q-A)

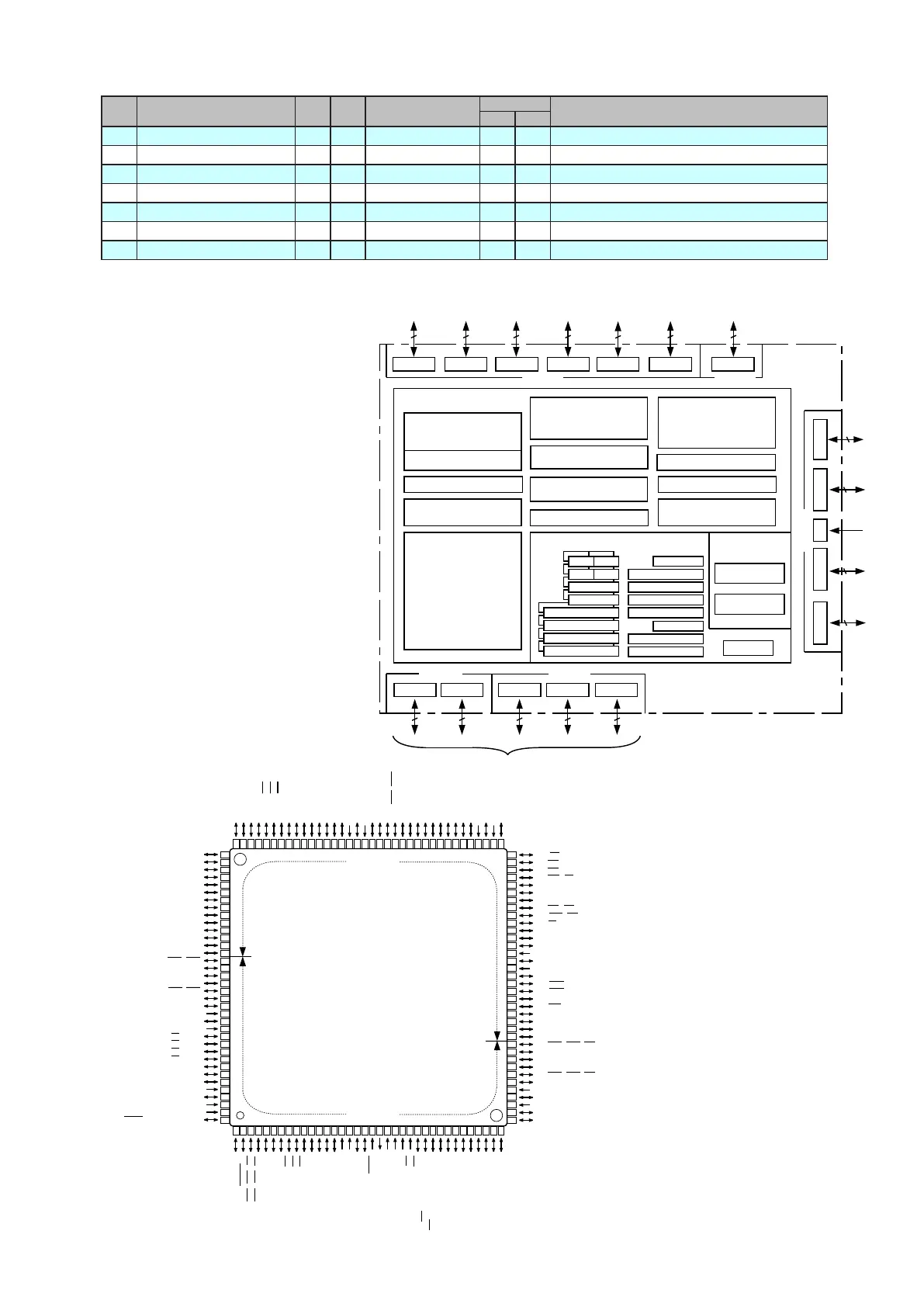

1.5 Pin Assignment

Figures 1.3 to 1.5 show pin assignments (top view).

Figure 1.3 Pin Assignment for 144-Pin Package

Pin

No

Port Name I/O Use Name

PortSetup

Note

Act. Init

58 P06/AN1/DA0 I/O I I_5V_CH5 - - Pull down to GND

59 VSS/AVSS I I GND - - GND

60 P07/AN0/DA1 I/O I I_5V_CH6 - - Pull down to GND

61 VREF I I +5VH - - +5V

62 VCC/AVCC I I +5VH - - +5V

63 P37/SSO I/O I/O HDMI_SDA - H HDMI Devices Control

64 P35/SCL/SSCK I/O SCL CPU_SCL - H Communication to Main CPU

IC11 : M3087BFLK [SR5003 : MAIN] / M3087BFL [SR6003 : MAIN]

Loading...

Loading...