2.1 Enhanced C67x+ CPU

2.2 Efficient Memory System

Aureus TMS320DA708, TMS320DA708B, TMS320DA788B

Floating-Point Digital Signal Processors

SPRS297E–JULY 2005–REVISED JULY 2007

The TMS320DA708/B/TMS320DA788B devices are the second generation of Texas Instruments'

Aureus™ family of high-performance 32-/64-bit floating-point digital signal processors.

Note: The TMS320DA788B supports DTS® 5.1, DTS-ES™ 6.1, DTS Neo:6™, DTS 96/24™, and DTS-ES

96/24™. If the application requires DTS algorithms, the TMS320DA788B DSP should be used.

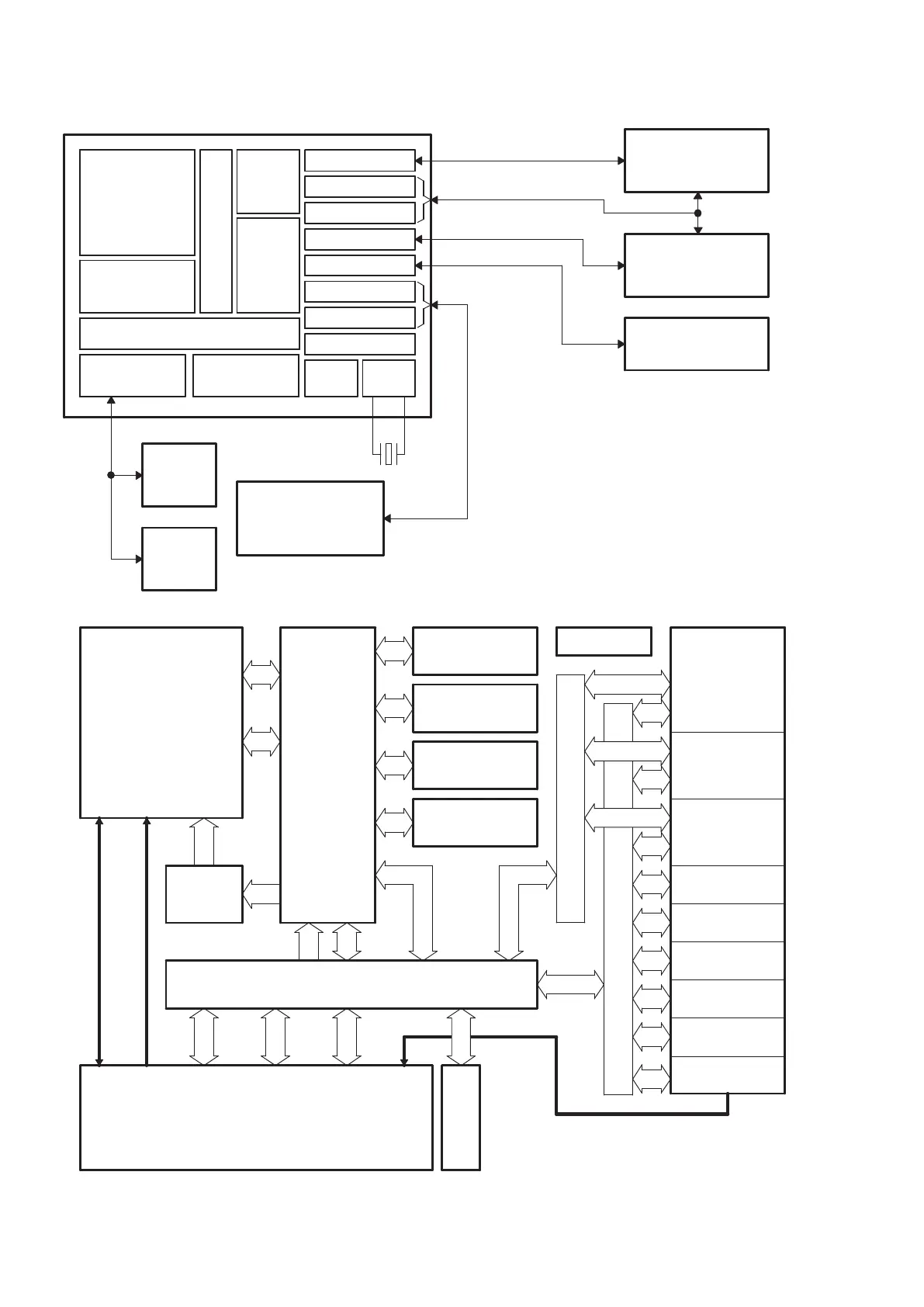

Figure 2-1 illustrates a high-level block diagram of the device and other devices to which it may typically

connect. An overview of each major block follows the figure.

Figure 2-1. DA708/B/DA788B Aureus™ Audio DSP System Diagram

The C67x+ CPU is an enhanced version of the C67x CPU used on the DA6xxx first-generation Aureus™

DSP. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and

floating-point performance per clock cycle. At 266 MHz, the CPU is capable of a maximum performance of

2128 MIPS/1596 MFLOPS by executing up to eight instructions (six of which are floating-point

instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision

floating-point, and 64-bit double-precision floating-point arithmetic.

The memory controller maps the large on-chip 256K-byte RAM and 768K-byte ROM as unified

program/data memory. Development is simplified since there is no fixed division between program and

data memory size as on some other devices.

The memory controller supports single-cycle data accesses from the C67x+ CPU to the RAM and ROM.

Up to four simultaneous accesses are supported:

Device Overview4 Submit Documentation Feedback

Aureus TMS320DA708, TMS320DA708B, TMS320DA788B

Floating-Point Digital Signal Processors

SPRS297E–JULY 2005–REVISED JULY 2007

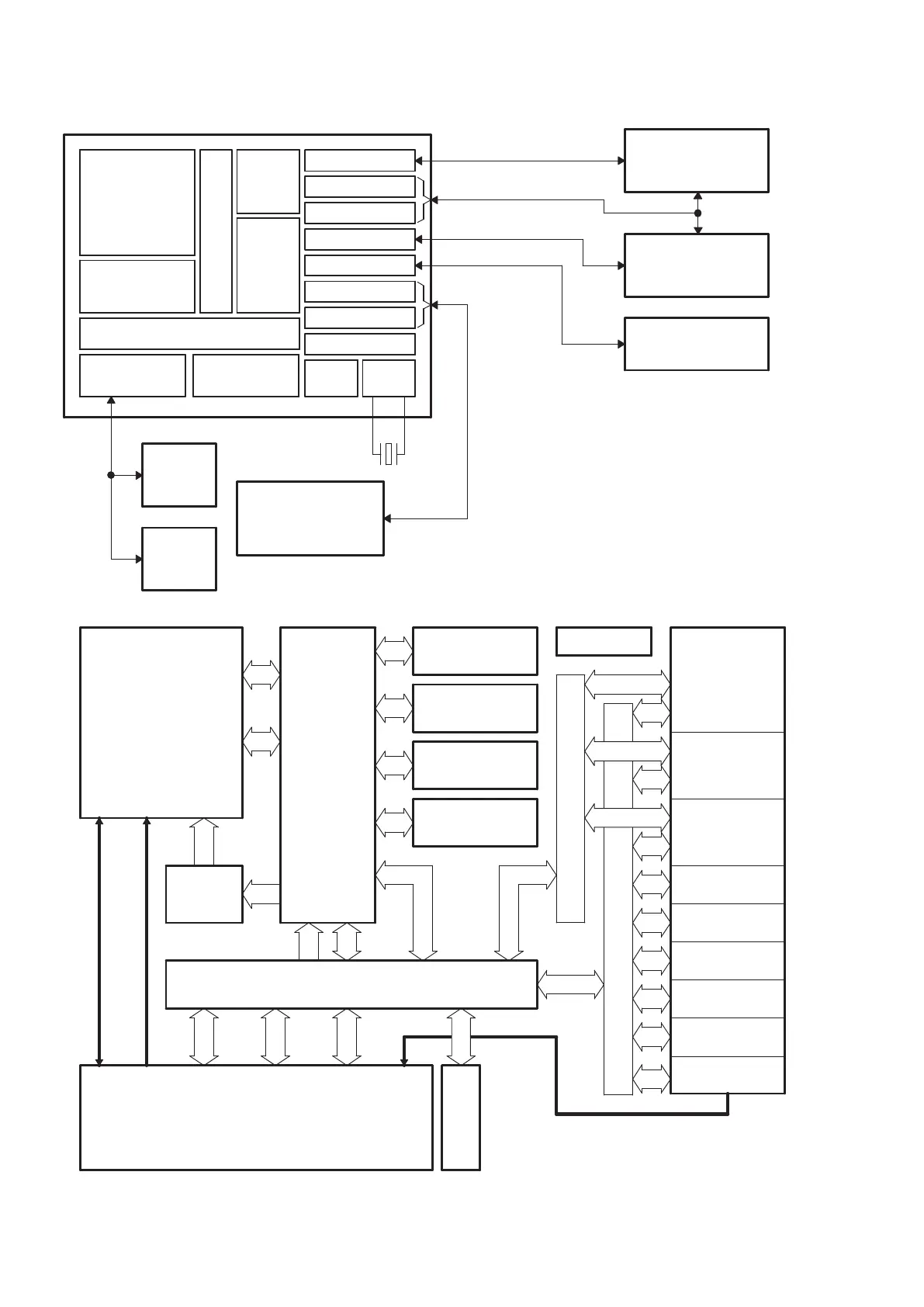

Figure 2-3. DA708/B/DA788B DSP Block Diagram

Submit Documentation Feedback Device Overview 13

Loading...

Loading...