8.1 mvHYPERION-CLx 33

IDC multi-pin connector 2 x 10 Pol RM 2.54 x 2.54 mm.

Note

Pins are not opto-isolated, feature no EMC filter and are not protected against overload and overvoltage.

Digital signals (pins 9-16) are LVTTL signals and not 5V tolerant. Failure to take this into account may

result in the destruction of the board.

Attention

Without an additional card with corresponding snubbers these signals must not conducted!

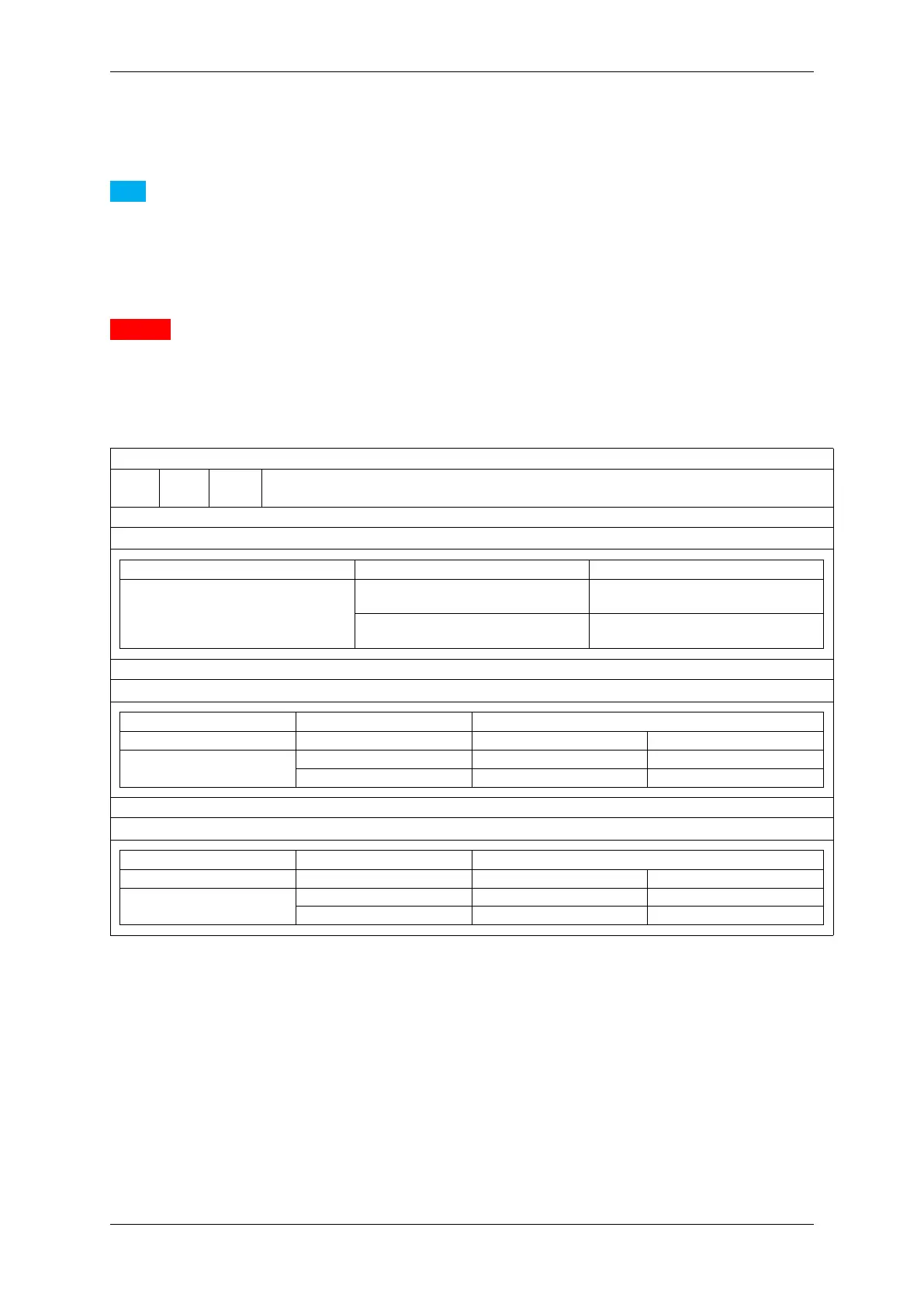

8.1.2.8 Switches

mvHYPERION

-CLb -CLe -CLm -

CLf

Switch S1

Flash memory

Position Comment

Def. Case of need FPGA version is

loaded (write protected)

User FPGA version, which can be

updated, is loaded.

Switch S2

Switch between TTL (5V) and PLC (24V) as well as Trigger and Sync on connector J3

Position Comment

Trigger (1) Sync (2)

on TTL (5V) TTL (5V)

off PLC (24V) PLC (24V)

Switch S3

Switch between TTL (5V) and PLC (24V) as well as Trigger and Sync on connector J4

Position Comment

Trigger (1) Sync (2)

on TTL (5V) TTL (5V)

off PLC (24V) PLC (24V)

MATRIX VISION GmbH

Loading...

Loading...