110

8575

8575

N/B Maintenance

N/B Maintenance

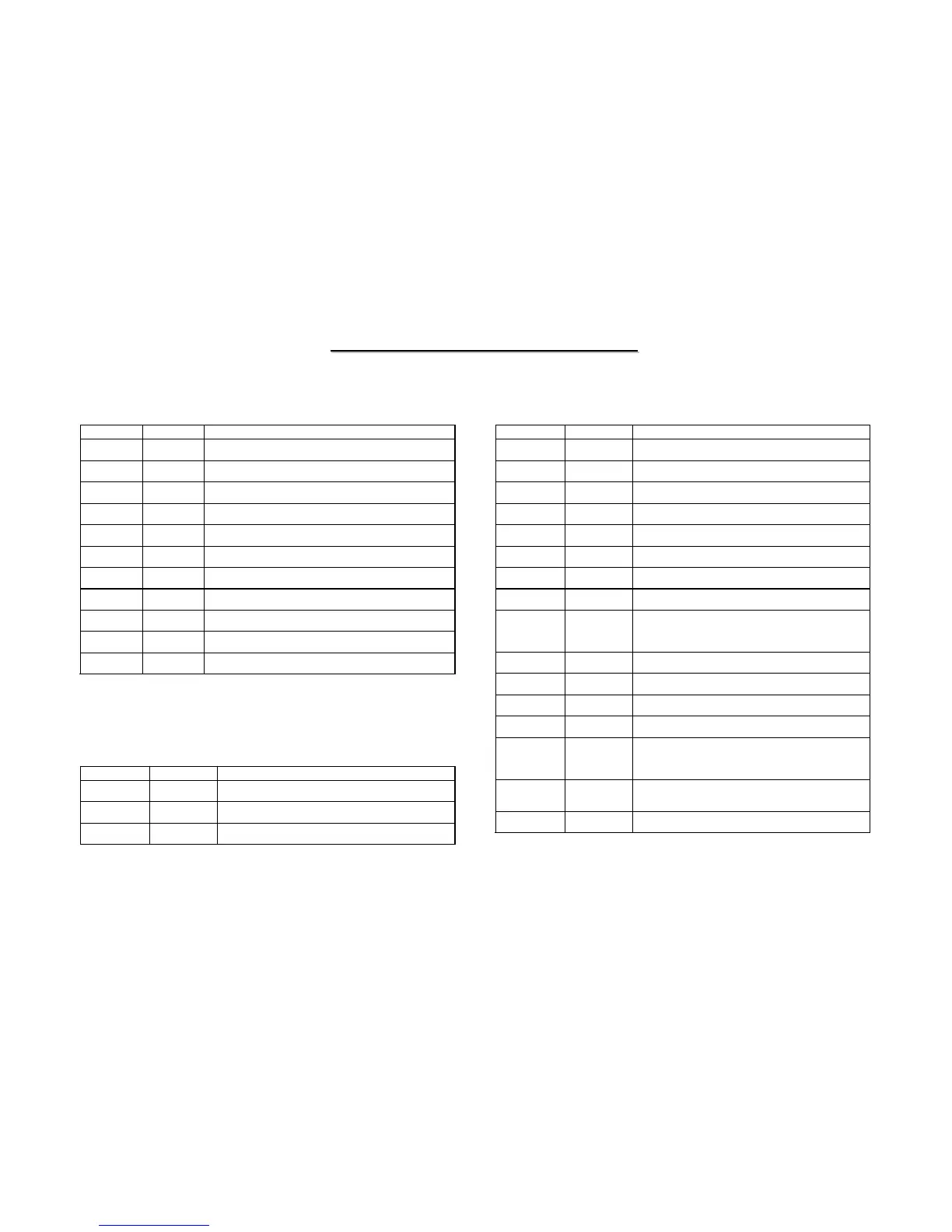

SiS MuTIOL Interface

Name Pin Attr Signal Description

AC/BE[3:0]

I/O

1.5V/3.3V - M

AGP Command/Byte Enable

APAR

I/O

1.5V/3.3V - M

AGP Parity

ST[2:0]

O

1.5V/3.3V - M

AGP Status Bus

PIPE#

I

1.5V/3.3V - M

AGP Pipeline Request

SBA[7:0]

I/O

1.5V/3.3V - M

Side Band Address

RBF#

I

1.5V/3.3V - M

Read Buffer Full

WBF#

I

1.5V/3.3V - M

Write Buffer Full

AD_STB[1:0]

I/O

1.5V/3.3V - M

AD Bus Strobe

AD_STB[1:0]#

I/O

1.5V/3.3V - M

AD Bus Strobe Compliment

SB_STB

I

1.5V/3.3V - M

Side Band Strobe

SB_STB#

I

1.5V/3.3V - M

Side Band Strobe Compliment

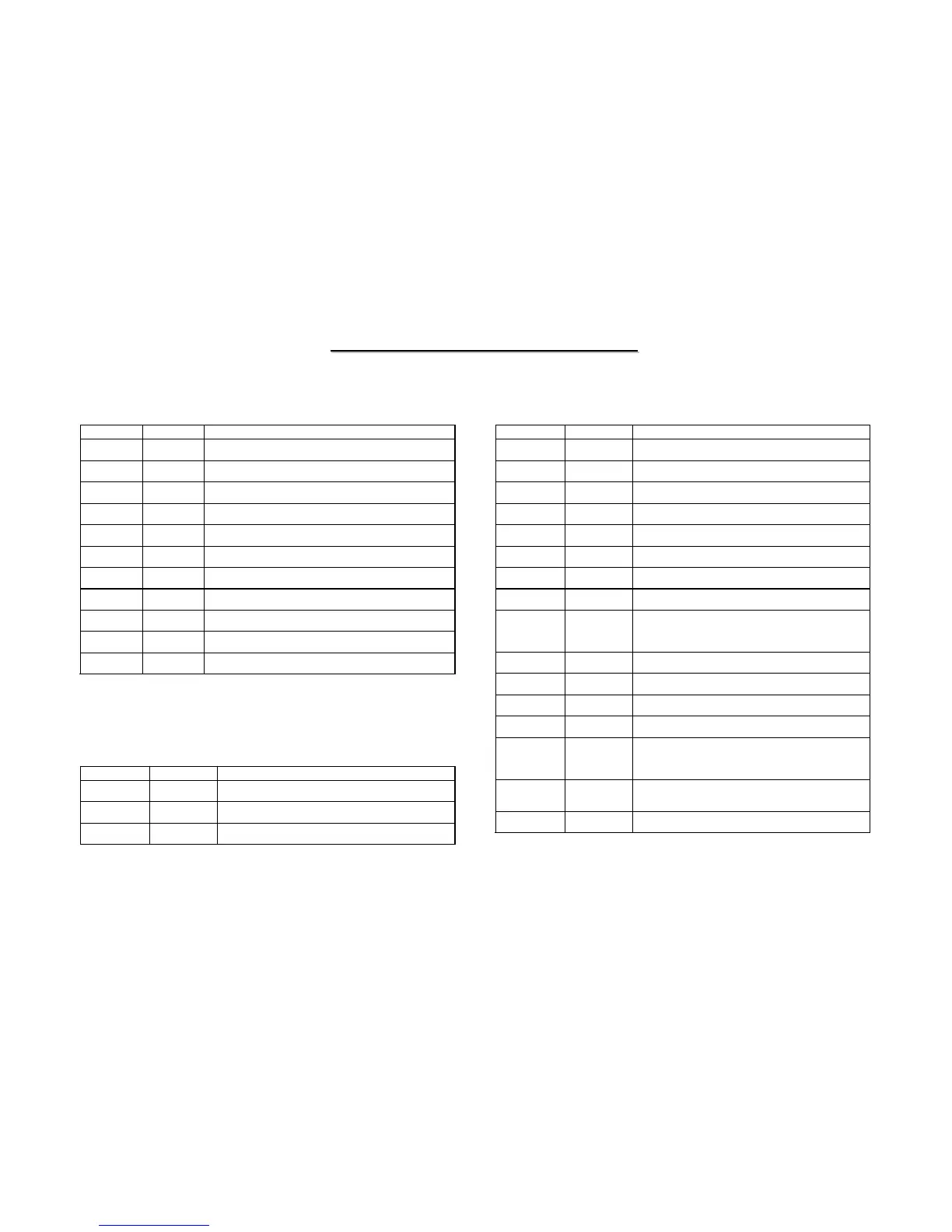

VB Interface

Name Pin Attr Signal Description

VBCLK

I

1.8V/3.3V - M

Channel B/A Clock Input

VBCLK multiplexed with SBA0

VBHCLK

O

1.8V/3.3V – M

VB Programming Interface Clock

VBHCLK multiplexed with RBF#

VBCAD

I/O

1.8V/3.3V – M

VB Programming Interface Data

VBCAD multiplexed with AREQ#

VBCTL[1:0]

O

1.8V/3.3V - M

VB Data Control

VBCTL[1:0] multiplexed with AAD[29:28]

VGPIO[3:2]

I/O

3.3V - M

VB GPIO pins

VGPIO[3:2] multiplexed with PIPE#/WBF#

VBHSYNC

I/O

1.8V/3.3V - M

Channel B H-Sync

VBHSYNC multiplexed with AAD30

VBVSYNC

I/O

1.8V/3.3V - M

Channel B V-Sync

VBVSYNC multiplexed with AAD31

VBDE

I/O

1.8V/3.3V - M

Channel B Data Valid

VBDE multiplexed with AAD27

VBGCLK

I/O

1.8V/3.3V - M

Channel B Clock Output.

This clock is used to trigger dual edge data transfer.

Perfect duty cycle is required.

VBGCLK multiplexed with AD_STB1

VBD[11:0]

I/O

1.8V/3.3V - M

Channel B Data

VBD[11:0] multiplexed with AAD

VAHSYNC

I/O

1.8V/3.3V - M

Channel A H-Sync

VAHSYNC multiplexed with AAD18

VAVSYNC

I/O

1.8V/3.3V - M

Channel A V-Sync

VAVSYNC multiplexed with AAD17

VADE

I/O

1.8V/3.3V - M

Channel A Data Valid

VADE multiplexed with AAD16

VAGCLK

I/O

1.8V/3.3V - M

Channel A Clock Output.

This clock is used to trigger dual edge data transfer.

Perfect duty cycle is required.

VAGCLK multiplexed with AD_STB0

VAGCLK#

I/O

1.8V/3.3V - M

Channel A Differential Clock Output. (To support

Chrontel).

VAGCLK# multiplexed with AD_STB0#

VAD[11:0]

I/O

1.8V/3.3V - M

Channel A Data

VAD[11:0] multiplexed with AAD

Stereo Glasses Interface

Name Pin Attr Signal Description

CSYNC

O

3.3V - M

Stereo Clock

RSYNC

O

3.3V - M

Stereo Right

LSYNC

O

3.3V - M

Stereo Left

5.2 SiS650 IGUI Host/Memory Controller

Loading...

Loading...