APPENDICES

APP - 37

MELSEC-

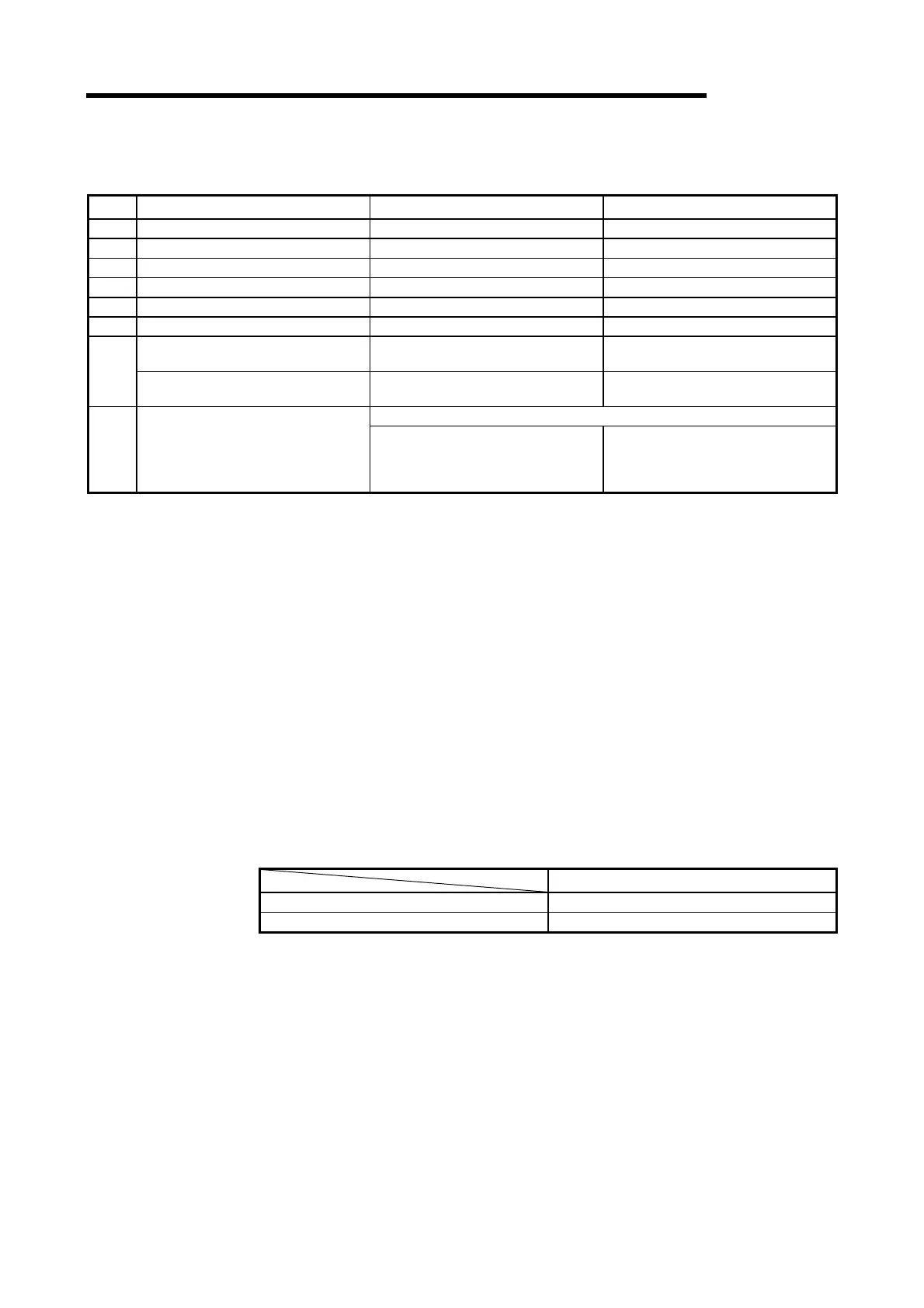

Appendix 3.2 Dissimilarities between A2SHCPU(-S1) and A2SCPU

The dissimilarities between the A2SHCPU(-S1) and A2SCPU are as follows :

Item A2SHCPU(-S1) A2SCPU

1 CPU processing speed *1 0.25

µ

s1

µ

s

2 I/O points 2048 points *2 512 points

3 File register capacity (R) Max. 8192 points (R0 to 8191) Max. 4096 points (R0 to 4095)

4 CC-Link dedicated instruction 8 None

5 Startup model A3 A2

6 Microcomputer program There are some restrictions. There is no restrictions.

7

Conventional memory cassette

A2SMCA-14KE/14KP

× {

New-type memory cassette

A2SNMCA-30KE

{{

Year, month, day, hour, minute, day of week (Automatic leap year calculation)

8 Clock precision

Precision

-3.1 to +5.3 s(TYP. +1.7 s)/d at 0 °C

-1.6 to +5.3 s(TYP. +2.4 s)/d at 25 °C

-9.6 to +3.6 s(TYP. -2.1 s)/d at 55 °C

Precision

-2.3 to +4.4 s(TYP. +1.8 s)/d at 0 °C

-1.1 to +4.4 s(TYP. +2.2 s)/d at 25 °C

-9.6 to +2.7 s(TYP. -2.4 s)/d at 55 °C

*1 : I/O processing : during refresh and LD instruction execution

*2 : Actual I/O points are the same as the AnS series, but this model has 2048 points of I/O device

for each CPU (X/Y0 to 7FF). The added I/O device can be used for MELSECNET (/B),

MELSECNET/MINI, or CC-Link.

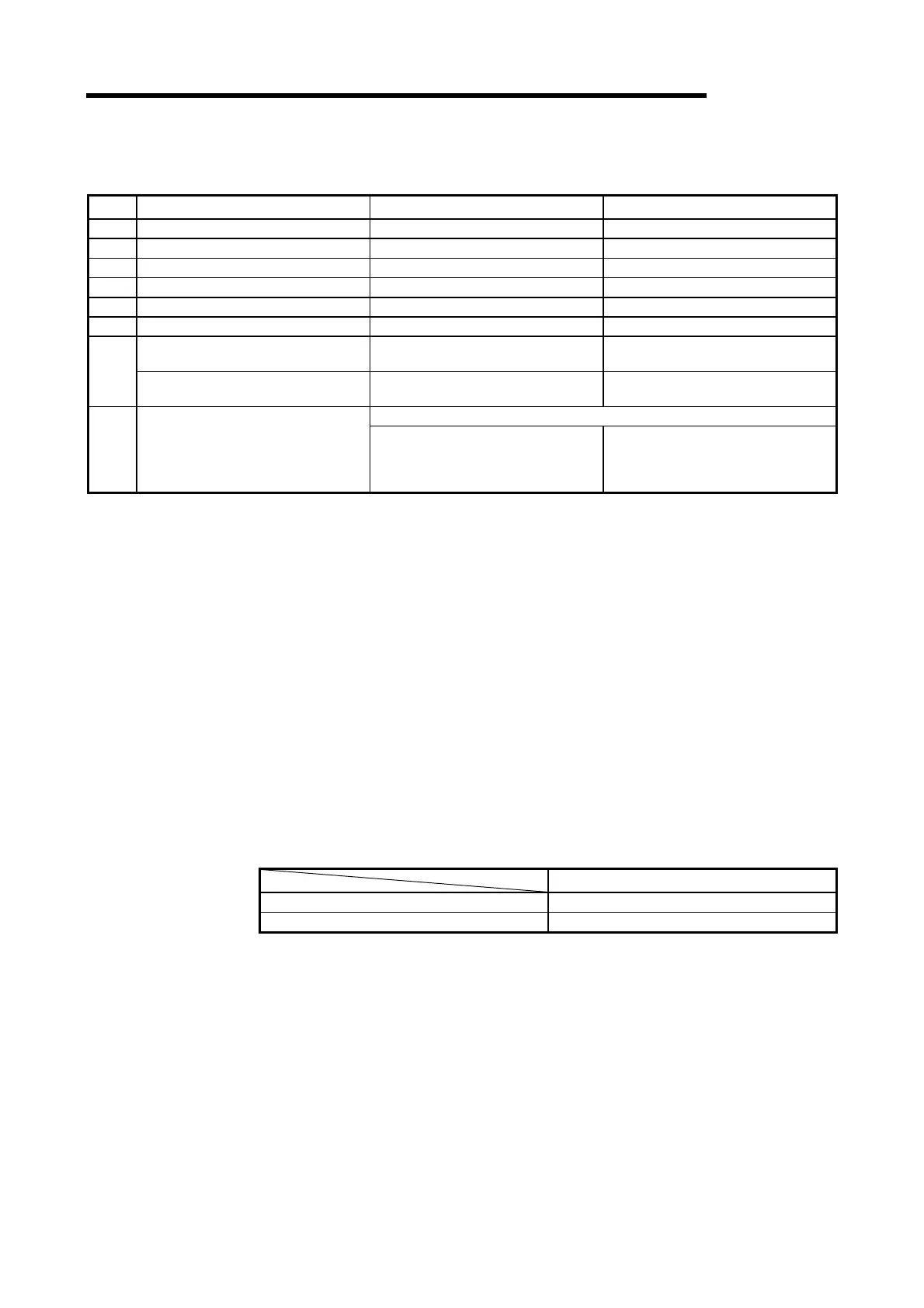

Appendix 3.3 Precautions when Switching the Model

Appendix 3.3.1 PLC type setting

The PLC type becomes "A3" to enable the use of 2048 input device points X/Y,

file register R8192 points and LEAD/LEDB instructions.

Appendix 3.3.2 The precaution when performing the ROM cutoff

When performing the ROM cutoff of A1SJHCPU and A1SHCPU with SW4GP-

GPPA, the startup model must be changed as following.

Startup model

Before software version Q A0J2H

Aafter software version R A1S

Loading...

Loading...