3-21

1

2

3

4

2

6

7

8

3.3 Indexing

(e) Index modification using extended data register (D) and extended link register (W) by

32 bits (Universal model QCPU(except Q00UJCPU) and LCPU.)

Like index modification using file register (ZR), index modification using extended data

register (D) and extended link register (W) by 32 bits can be performed by the following

two methods.

• Specifing the index registers’ range used for indexing with 32-bit.

• Specifing the 32-bit indexing using “ZZ” specification.

32-bit indexing with the "ZZ" specification is only available for the following CPU

modules. See the programming tool operating manual for the available

programming tools.

• The first five digits of the serial No. for QnU(D)(H)CPU is “10042” or higher.

(except Q00UJCPU)

• QnUDE(H)CPU

•LCPU

(6) Cautions

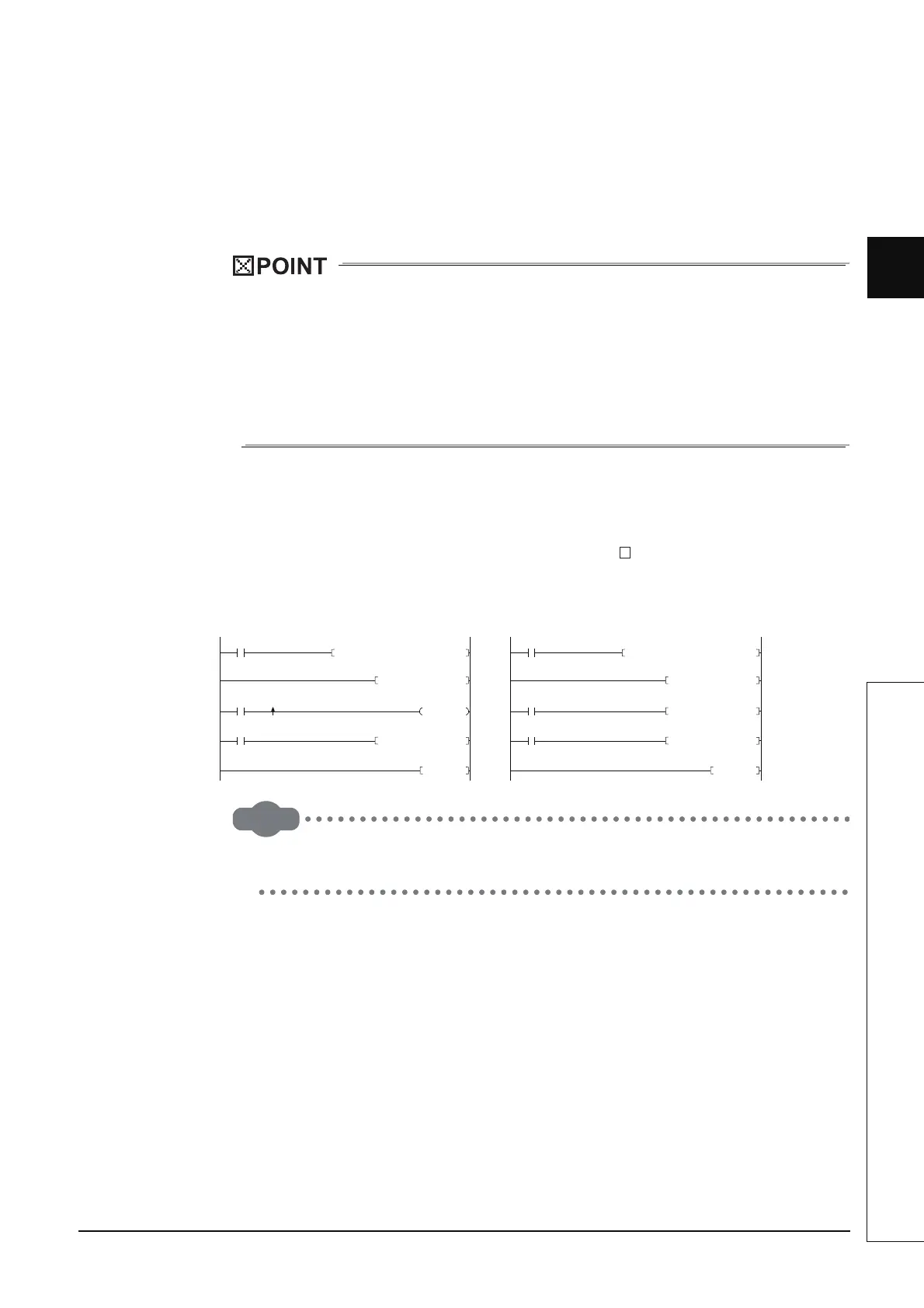

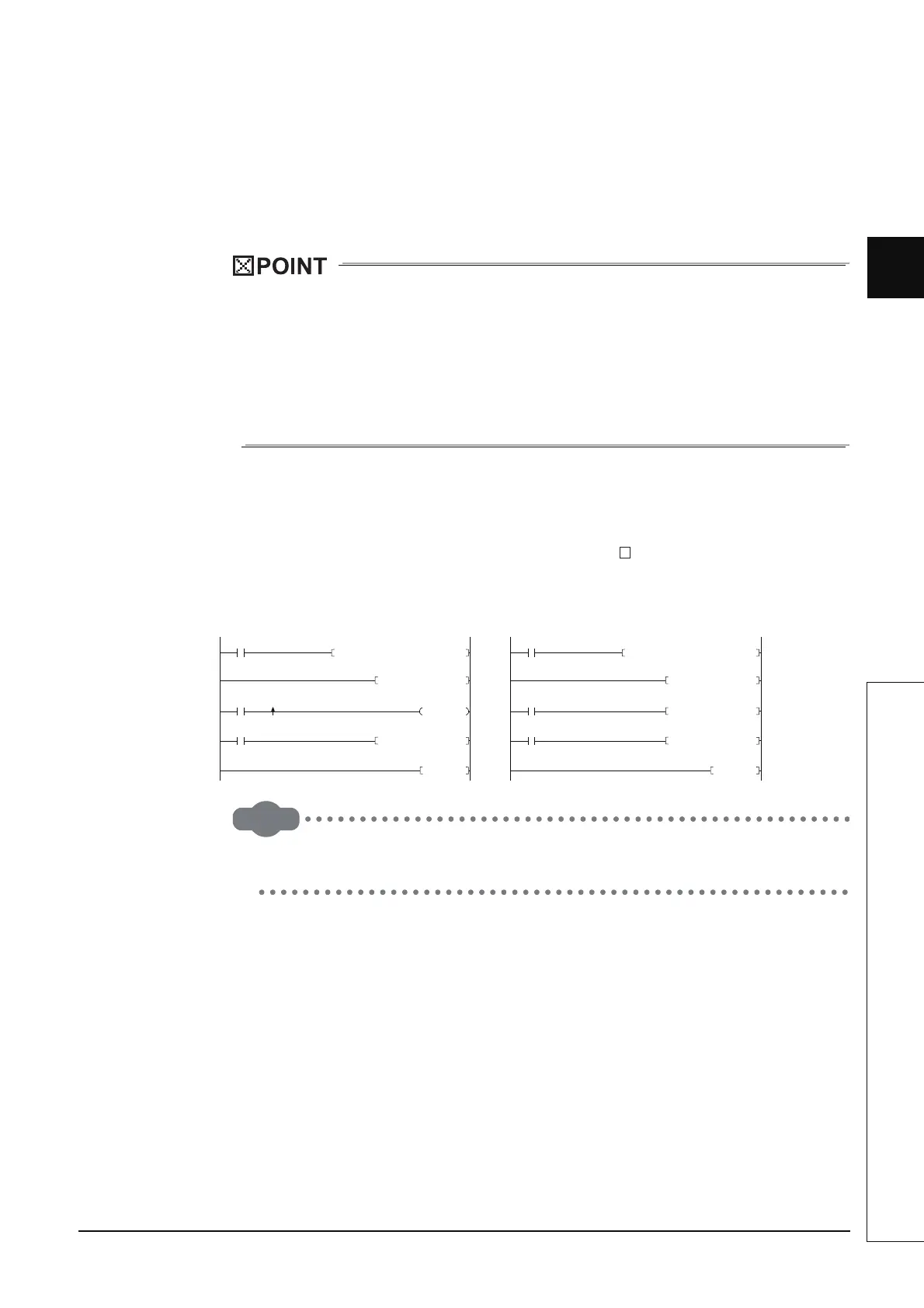

(a) Performing indexing between the FOR and NEXT instructions

Pulses can be output between the FOR and NEXT instructions by use of the edge relay

(V). However, pulse output using the PLS/PLF/pulse ( P) instruction is not allowed.

[When edge relay is used] [When edge relay is not used]

(M0Z1 provides normal pulse output.) (M0Z1 does not provide normal pulse output.)

Remark

The ON/OFF data of X0Z1 is stored by the edge relay V0Z1.

For example, the ON/OFF data of X0 is stored by V0, and that of X1 by V1.

SM400

X0Z1

Z1

M0Z1

NEXT

K0MOV

K10FOR

V0Z1

Z1INC

SM400

SM400

X0Z1

Z1

NEXT

K0MOV

K10FOR

Z1INC

SM400

M0Z1PLS

Loading...

Loading...