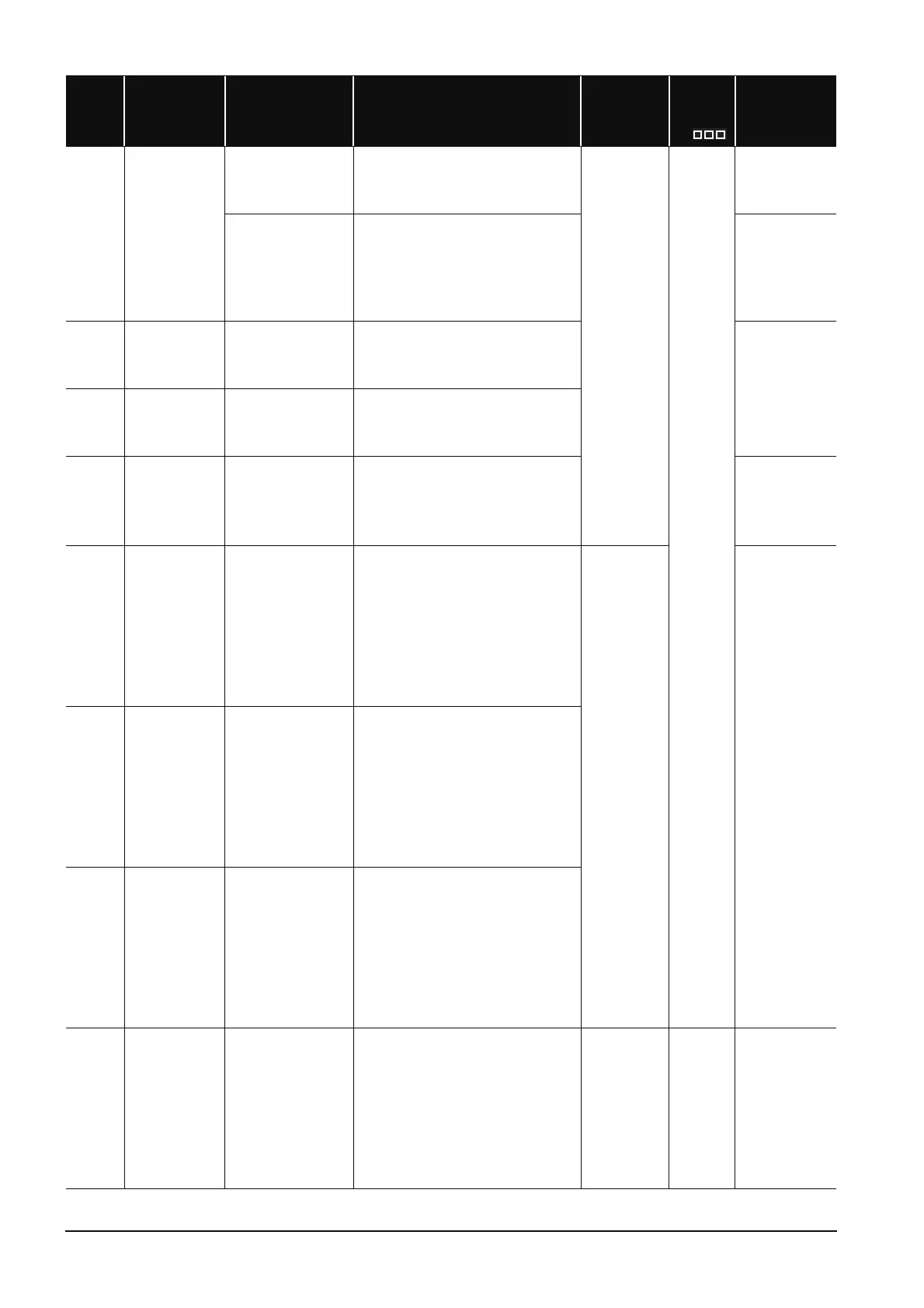

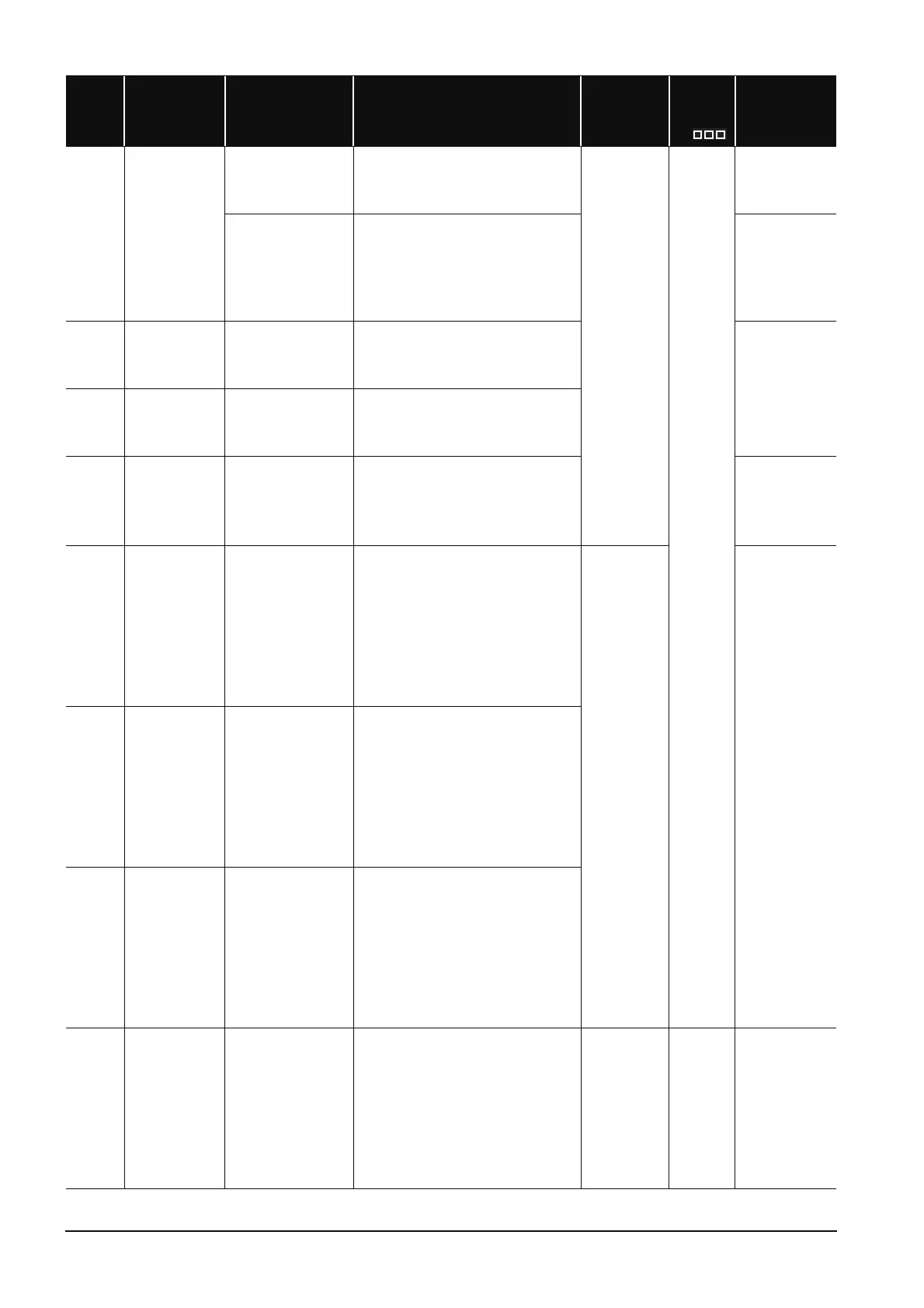

App-166

SM775

Selection of

refresh

processing during

COM/CCOM

instruction

execution

OFF : Performs link

refresh

ON : Performs no link

refresh

Select whether link refresh processing will be

performed or not when only communication

with the CPU module is made at the

execution of the COM instruction.

U

New

Q00J/Q00/Q01

Qn(H)

QnPH

OFF : Performs refresh

processes other

than an I/O

refresh

ON : Performs refresh

set by SD778

Select whether to perform refresh processes

other than an I/O refresh set by SD778 when

the COM or CCOM instruction is executed.

Q00J/Q00/Q01

*1

Qn(H)

*7

QnPH

*4

QnPRH

QnU

LCPU

SM776

Enable/disable

local device at

CALL

OFF : Local device

disabled

ON : Local device

enabled

Set whether the local device of the

subroutine program called at execution of

the CALL instruction is valid or invalid.

Qn(H)

QnPH

QnPRH

QnU

*10

LCPU

SM777

Enable/disable

local device in

interrupt program

OFF : Local device

disabled

ON : Local device

enabled

Set whether the local device at execution of

the interrupt program is valid or invalid.

SM794

PID bumpless

processing(for

incomplete

derivative)

OFF : Matched

ON : Not matched

Specifies whether to match the set value

(SV) with the process value (PV) or not in

the manual mode.

Q00J/Q00/Q01

*1

Qn(H)

*8

QnPRH

QnU

LCPU

SM796

Block information

using multiple

CPU high-speed

transmission

dedicated

instruction (for

CPU No.1)

OFF : Block is secured

ON : Block set by

SD796 cannot be

secured

This relay turns on when the number of the

remaining blocks in the dedicated instruction

transmission area used for the multiple CPU

high-speed transmission dedicated

instruction (target CPU= CPU No.1) is less

than the number of blocks specified in

SD796. This relay is on when an instruction

is executed, and is off while an END

processing is being executed or when free

space is available in the area.

S (When

instruction/END

processing

executed)

QnU

*9

SM797

Block information

using multiple

CPU high-speed

transmission

dedicated

instruction (for

CPU No.2)

OFF : Block is secured

ON : Block set by

SD797 cannot be

secured

This relay turns on when the number of the

remaining blocks in the dedicated instruction

transmission area used for the multiple CPU

high-speed transmission dedicated

instruction (target CPU= CPU No.2) is less

than the number of blocks specified in

SD797. This relay is on when an instruction

is executed, and is off while an END

processing is being executed or when free

space is available in the area.

SM798

Block information

using multiple

CPU high-speed

transmission

dedicated

instruction (for

CPU No.3)

OFF : Block is secured

ON : Block set by

SD798 cannot be

secured

This relay turns on when the number of the

remaining blocks in the dedicated instruction

transmission area used for the multiple CPU

high-speed transmission dedicated

instruction (target CPU= CPU No.3) is less

than the number of blocks specified in

SD798. This relay is on when an instruction

is executed, and is off while an END

processing is being executed or when free

space is available in the area.

SM799

Block information

using multiple

CPU high-speed

transmission

dedicated

instruction (for

CPU No.4)

OFF : Block is secured

ON : Block set by

SD799 cannot be

secured

This relay turns on when the number of the

remaining blocks in the dedicated instruction

transmission area used for the multiple CPU

high-speed transmission dedicated

instruction (target CPU= CPU No.) is less

than the number of blocks specified in

SD799. This relay is on when an instruction

is executed, and is off while an END

processing is being executed or when free

space is available in the area.

S (When

instruction/END

processing

executed)

New

QnU

*9

Number Name

Meaning

Explanation

Set by

(When Set)

Corres-

ponding

ACPU

M9

Corresponding

CPU

Loading...

Loading...