5.1 Boot mode selection

The internal ROM memory is used to store the boot code. After a reset, the Arm processor starts its code execution from this

memory. The bootloader code is executed every time the part is powered-ON, is reset, or wakes up from a deep power-down while

in a low power mode.

Depending on the values of the CMPA bits, ISP pin, and the image header type definition, the bootloader decides whether to boot

from internal flash or run into ISP mode. See Section 6.5 FFR region definitions in

LPC55S6x/LPC55S2x/LPC552x User manual

(document UM11126).

The state of port pin, PIO0_5, at Reset determines the boot source of the part or if the handler is invoked. The LPC55S6x/

LPC55S2x/LPC552x/55S1x will read status of the ISP pins to determine boot source, as shown in

Table 8 .

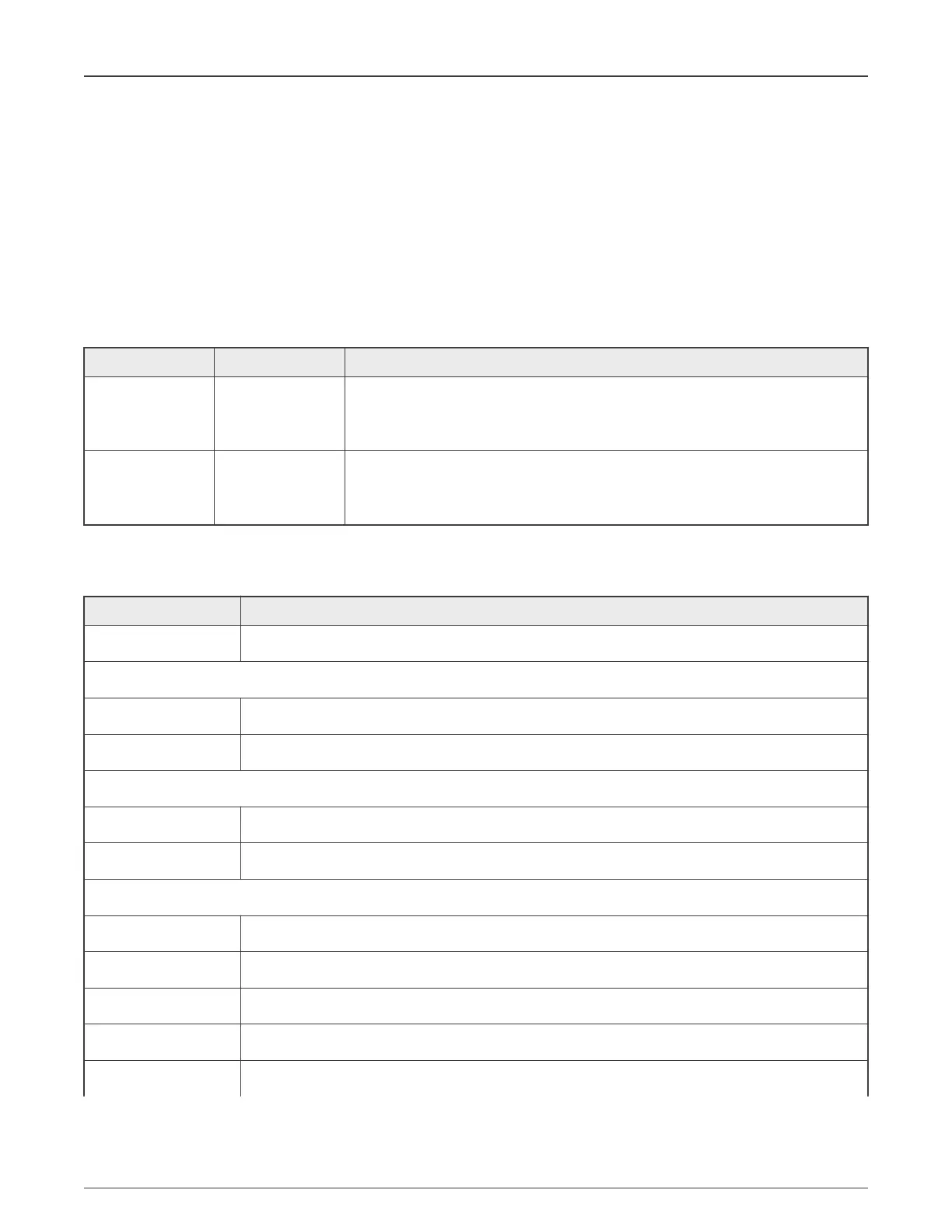

Table 8. Boot mode and ISP download modes based on ISP pins

Boot mode ISP0 (PIO0_5 pin) Description

Passive boot HIGH

The LPC55S6x/LPC55S2x/LPC552x will look for valid image in the internal flash,

if no valid image is found, the LPC55S6x/LPC55S2x/LPC552x will enter ISP boot

mode based on DEFAULT_ISP_MODE bits defined in Table 9.

ISP boot LOW

One of the serial interfaces (UART0, I2C1, SPI3, HS_SPI, USB0, USB1) is used

to download image from host into internal flash. The first valid probe message on

USART, I2C, SPI or USB locks in that interface.

Table 9 shows the ISP pin assignments and is the default pin assignment used by the ROM code that cannot be changed.

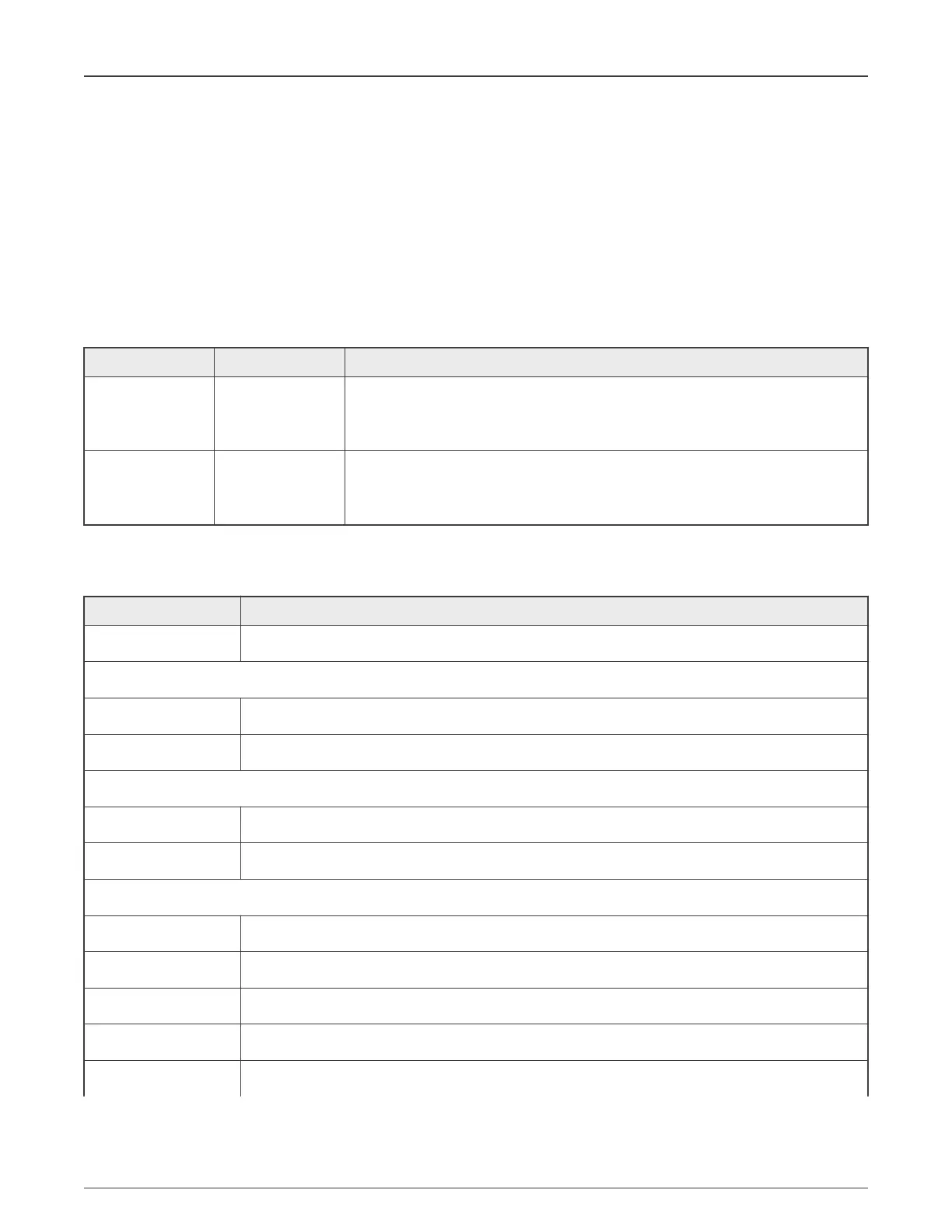

Table 9. ISP pin assignment

ISP pin Port pin assignment

ISP0 PIO0_5

USART_ISP mode

FC0_TXD PIO0_30

FC0_RXD PIO0_29

I2C_ISP mode

FC1_SDA PIO0_13

FC1_SCL PIO0_14

SPI ISP mode

FC3_SCK PIO0_6

FC3_SSEL0 PIO0_4

FC3_MISO PIO0_2

FC3_MOSI PIO0_3

HS_SPI_SCK PIO1_2

Table continues on the next page...

NXP Semiconductors

Boot mode configurations

Hardware Design Guidelines for LPC55(S)xx Microcontrollers, Rev. 0, 30 October 2020

Application Note 11 / 24

Loading...

Loading...