8: Firmware and Advanced Communications

225-00000-000-11-201604 101

program needs to delay for this length of time before issuing another command. In some

instances, other commands will also write to these registers (i.e., integration time), in these

cases the user has the options of setting the parameters through 2 different methods.

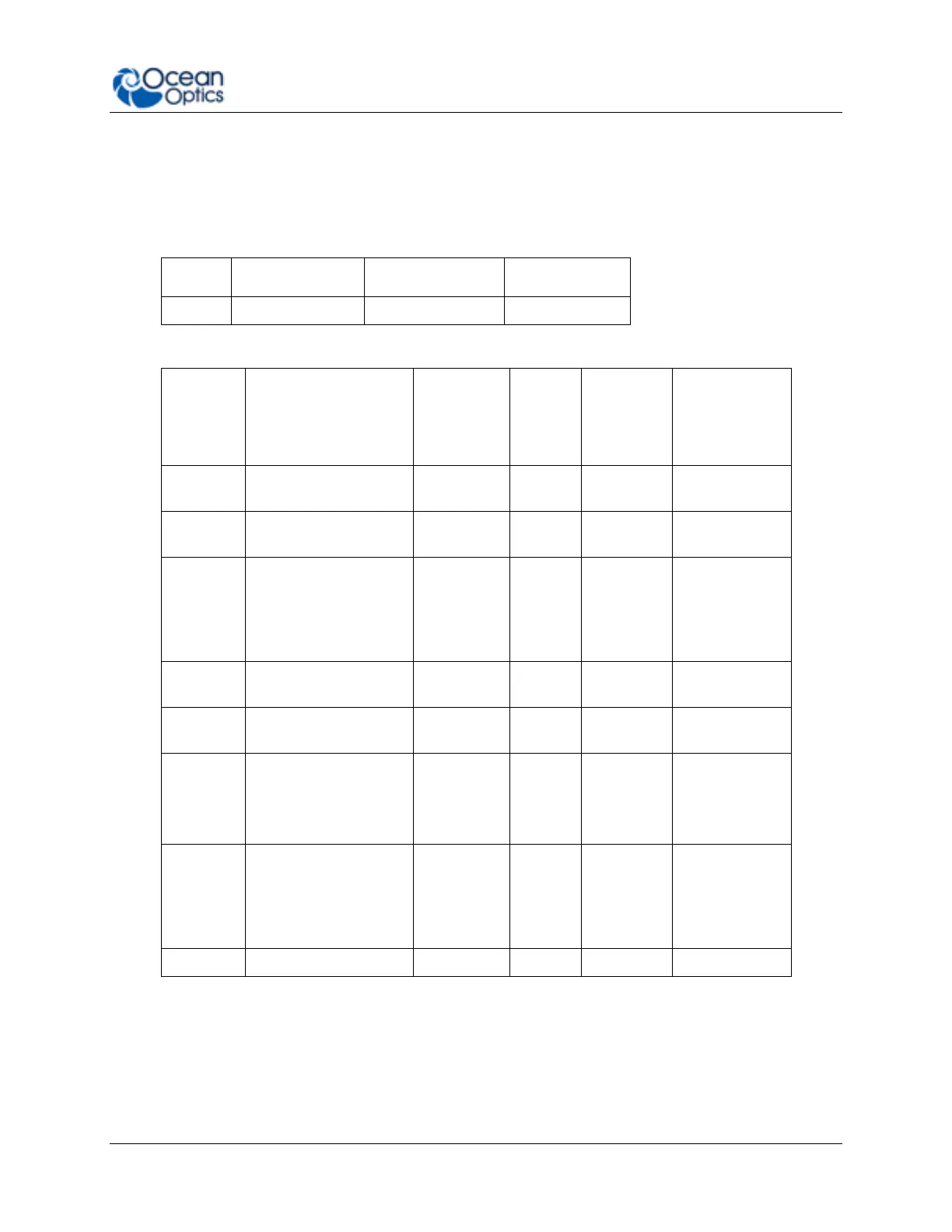

Byte Format

Master Clock Counter

Divisor

FPGA Firmware

Version (Read Only)

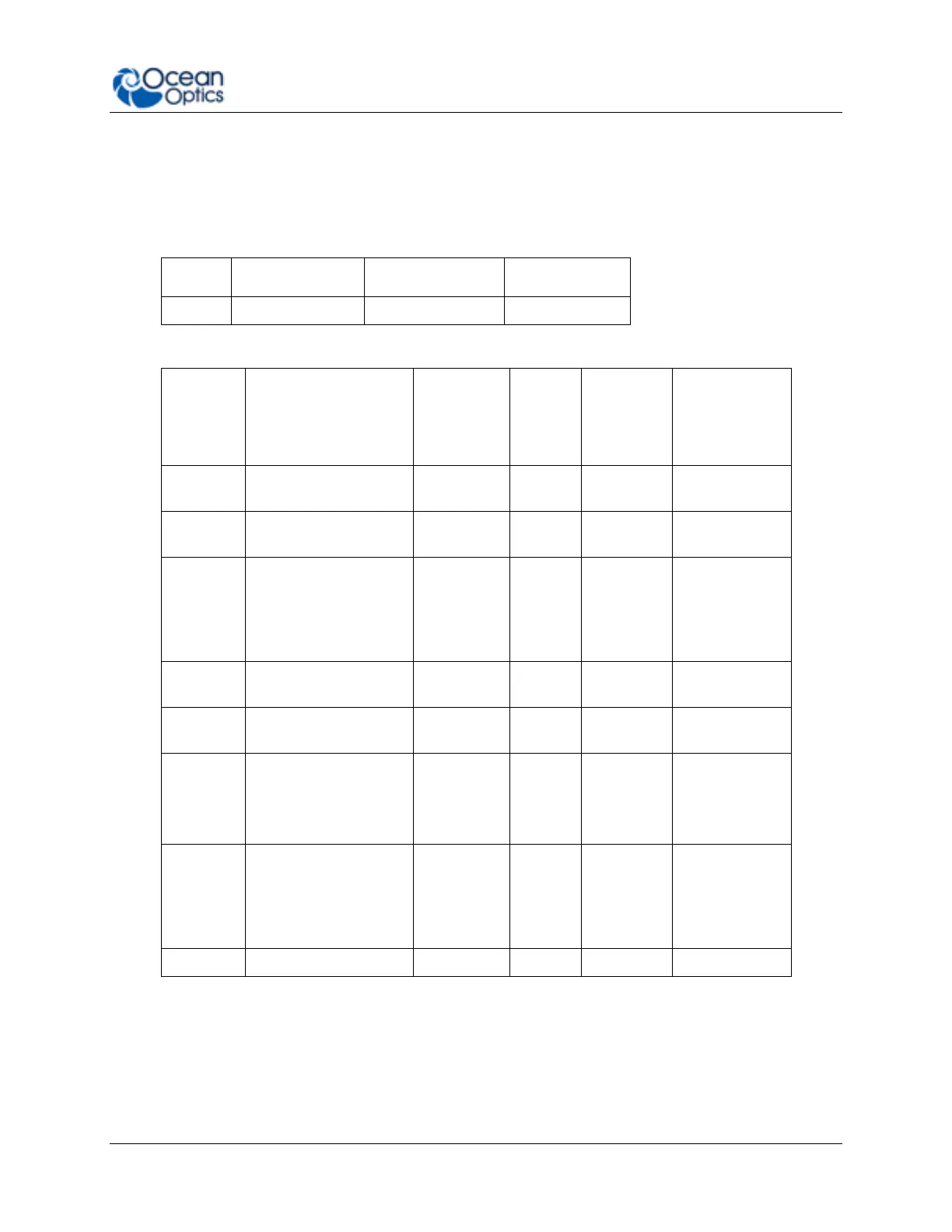

Continuous Strobe

Timer Interval Divisor

Continuous

Strobe Base

Clock

(see Register

0x0C)

Continuous Strobe

Base Clock Divisor

Integration Period

Base Clock Divisor

Set base_clk or

base_clkx2

0: base_clk

1: base_clkx2

Integration Clock

Timer Divisor

Integration

Period Base

Clock

(see Register

0x10)

Loading...

Loading...