8: Firmware and Advanced Communications

78 225-00000-000-11-201604

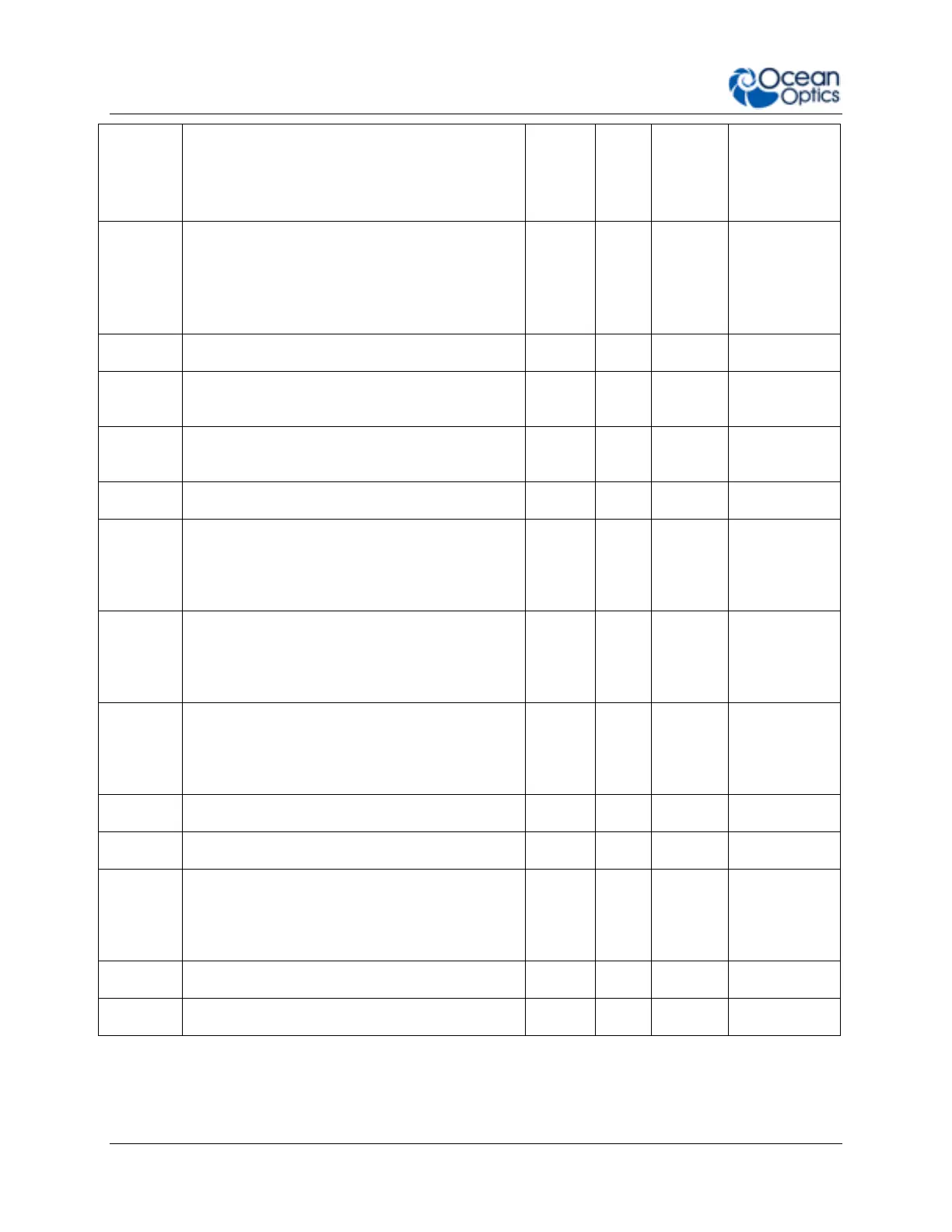

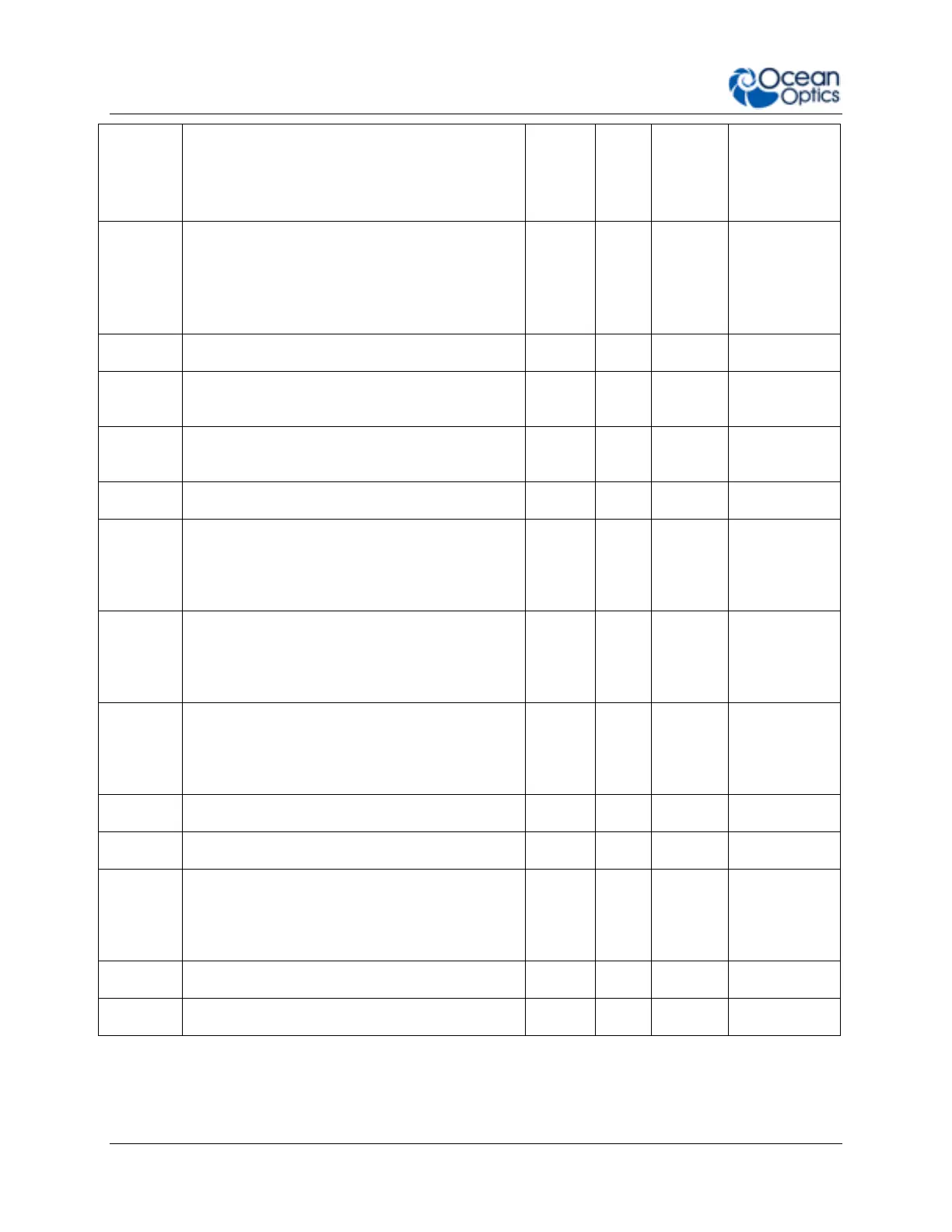

Trigger Mode

0 = Free Running

1 = External Hardware Level Trigger

1 = External Synchronization Trigger

3 = External Hardware Edge Trigger

Single Strobe High Clock Transition Delay

Count

Single Strobe Low Clock Transition Delay

Count

GPIO Mux Register

0: pin is GPIO pin

1: pin is alternate function

GPIO Output Enable

1: pin is output

0: pin is input

GPIO Data Register

For Output: Write value of signal

For Input: Read current GPIO state

Offset Control

Bit 0 = Enable Auto-Nulling

Bit 1 = Enable Auto-Nulling Saturation

FPGA Programmed (Read Only)

Loading...

Loading...