Automotive Module Series

AG525R-GL QuecOpen

Hardware Design

AG525R-GL_QuecOpen_Hardware_Design 55 / 104

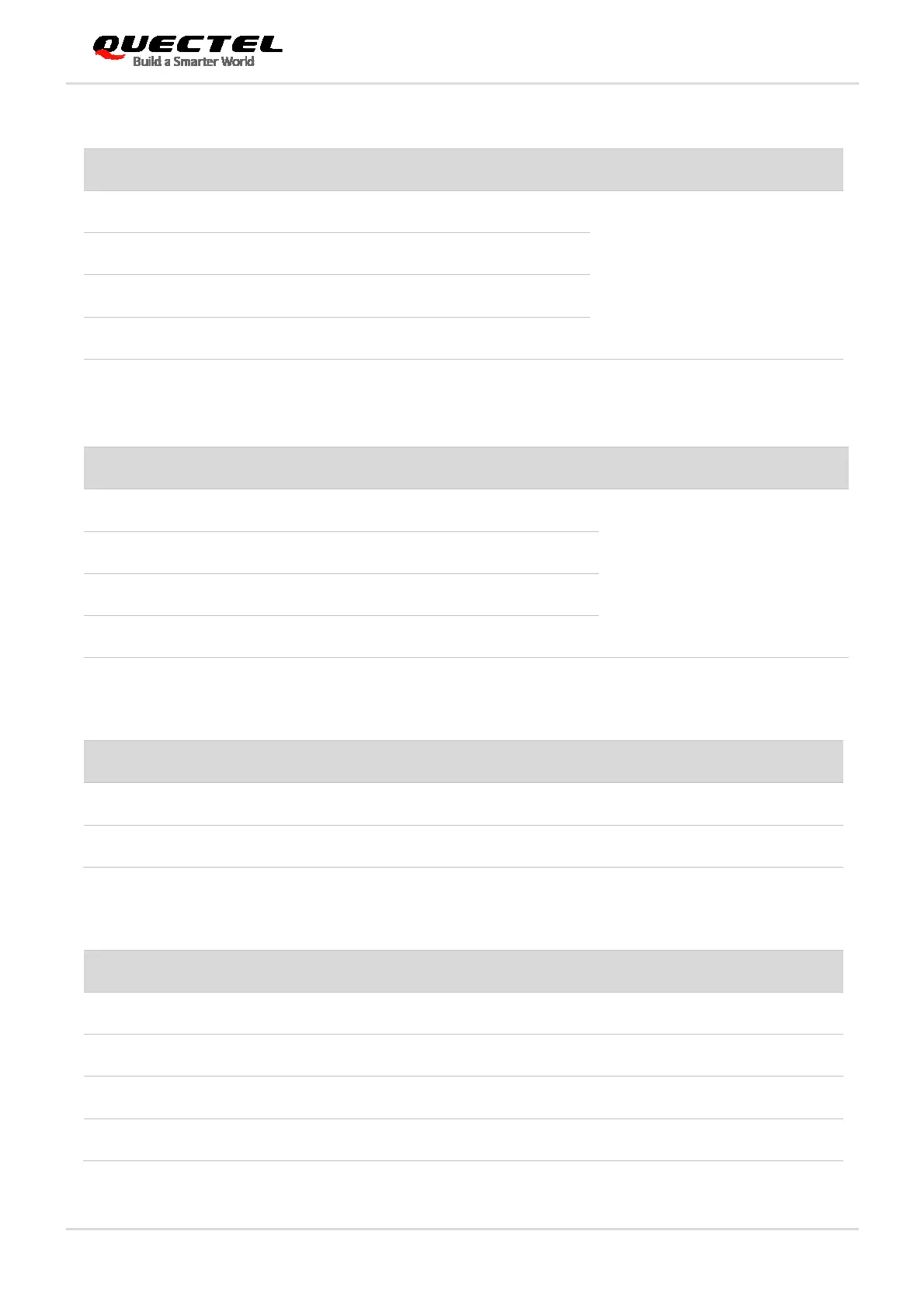

Table 13: Pin Definition of UART1 Interface

Pin Name Pin No. I/O Description Comment

UART1_CTS 71 DO UART1 clear to send

1.8 V power domain.

Can be configured to GPIOs.

UART1_RTS 74 DI UART1 request to send

UART1_TXD 70 DO UART1 transmit

UART1_RXD 72 DI UART1 receive

Table 14: Pin Definition of BT UART Interface

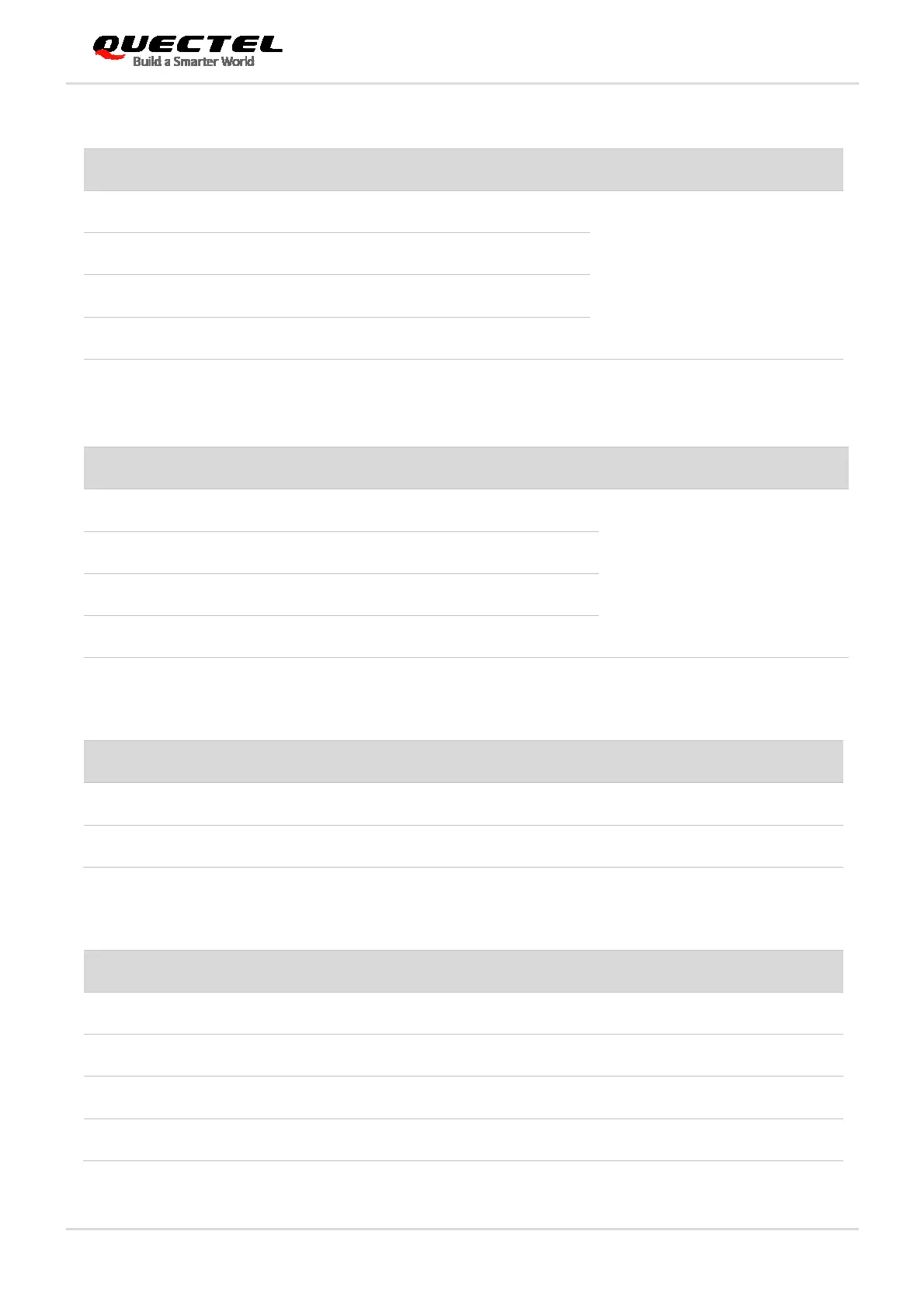

Table 15: Pin Definition of Debug UART Interface

Pin Name Pin No. I/O Description Comment

DBG_TXD 107 DO Debug UART transmit 1.8 V power domain.

DBG_RXD 110 DI Debug UART receive 1.8 V power domain.

Table 16: Logic Levels of Digital I/O

Parameter Min. Max. Unit

V

IL

-0.3 0.63 V

V

IH

1.17 2.1 V

V

OL

0 0.45 V

V

OH

1.35 1.8 V

Pin Name Pin No. I/O Description Comment

BT_UART_TXD 59 DO BT UART transmit

1.8 V power domain.

Can be configured to GPIOs

BT_UART_RXD 63 DI BT UART receive

BT_UART_RTS 61 DI BT UART request to send

BT_UART_CTS 62 DO BT UART clear to send

Loading...

Loading...