Automotive Module Series

AG525R-GL QuecOpen

Hardware Design

AG525R-GL_QuecOpen_Hardware_Design 60 / 104

3.14. SPI Interfaces

The module provides two SPI interfaces supporting only master mode. The maximum clock frequency of

SPI is up to 50 MHz.

Table 20: Pin Definition of SPI Interfaces

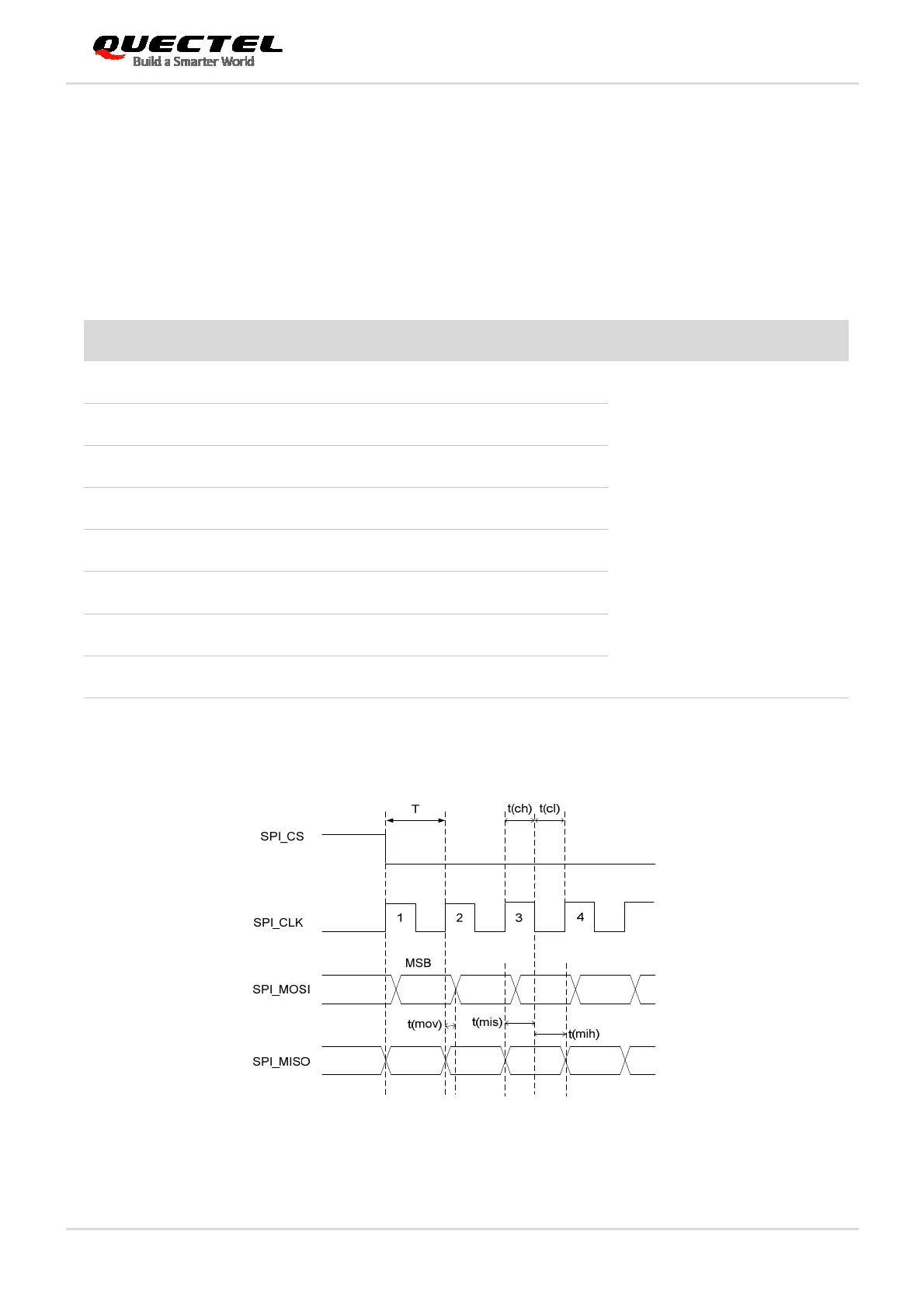

The following figure shows the timing relationship of SPI interfaces. The related parameters of SPI timing

are shown in the table below.

Figure 26: SPI Timing

Pin Name Pin No. I/O Description Comment

SPI1_CLK 216 DO SPI1 clock

1.8 V power domain.

Can be configured to GPIO.

If unused, keep them open.

SPI1_CS 213 DO SPI1 chip select

SPI1_MISO 219 DI SPI1 master-in salve-out

SPI1_MOSI 210 DO SPI1 master-out slave-in

SPI2_CLK 103 DO SPI2 clock

SPI2_CS 105 DO SPI2 chip select

SPI2_MISO 106 DI SPI2 master-in salve-out

SPI2_MOSI 108 DO SPI2 master-out slave-in

Loading...

Loading...