5G Module Series

RM500Q-GL Hardware Design

RM500Q-GL_Hardware_Design 45 / 85

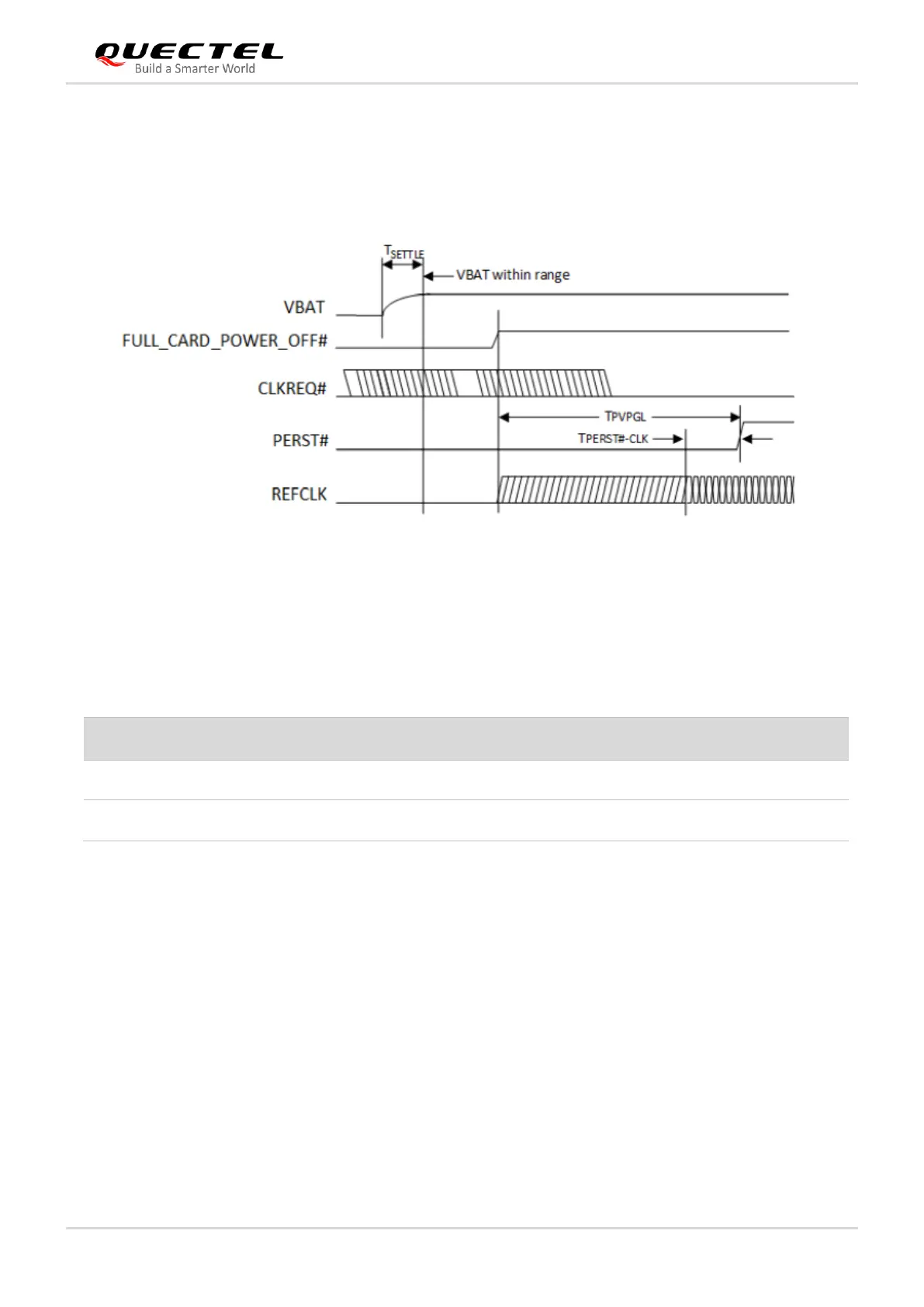

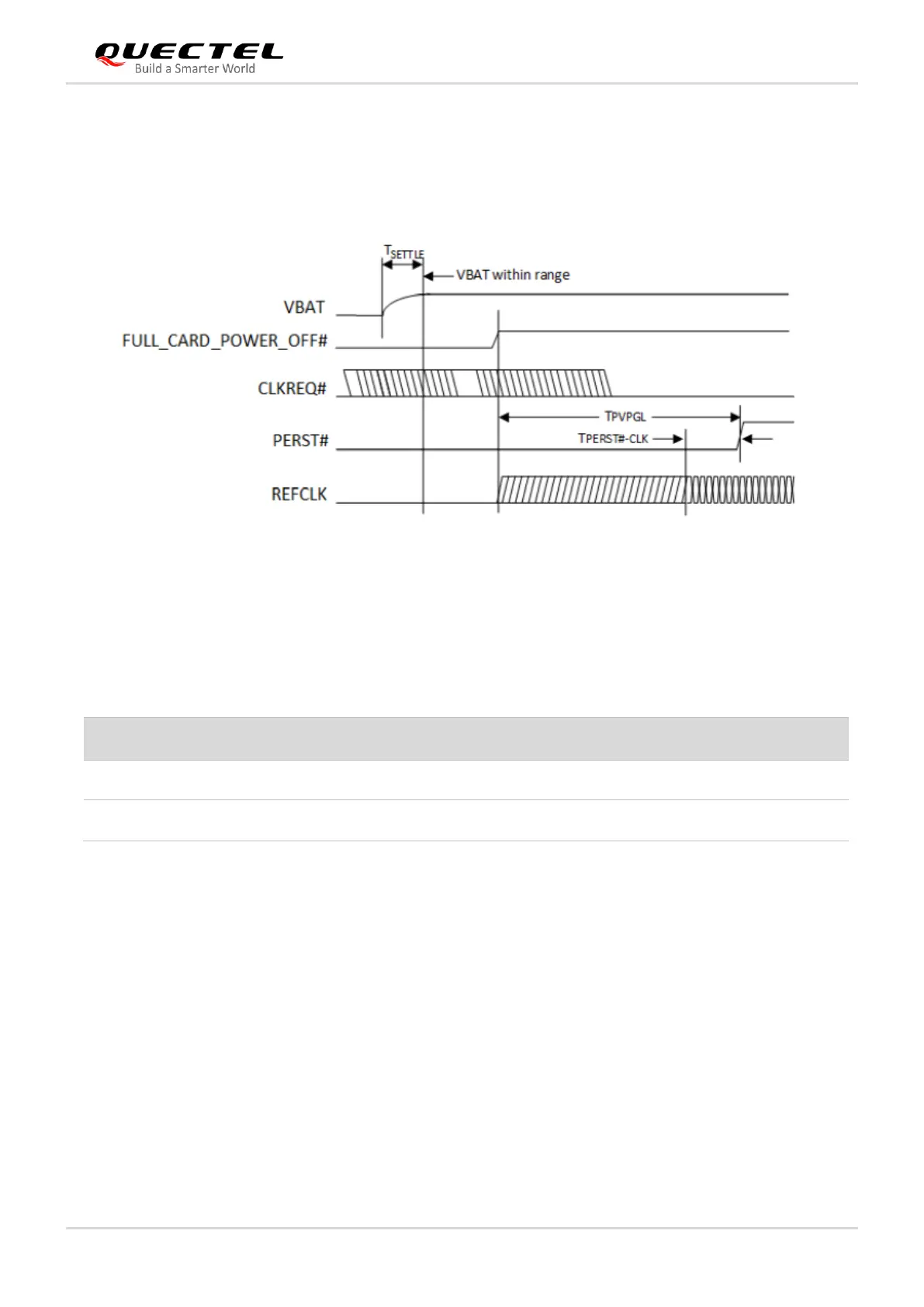

4.3.4. PCIe Timing

The following figure is PCIe power-up timing sequence for an adapter powered from system power rail in

PCI Express M.2 specification.

Figure 20: PCIe Power-on Timing Requirements of M.2 Specification

The following table is power-up timing variables in PCI Express M.2 specification.

Table 17: Power-up Timing of M.2 Specification

Loading...

Loading...